# **SYNOPSYS**®

Opportunities for Optics into the Datacenter and High-Performance Computing (HPC) Infrastructure

\*\*Accelerating PIC Adoption in Established Markets\*\*

Jigesh Patel, Remco Stoffer\*

April 17, 2024 – PIC International – Brussels (Belgium)

## CONFIDENTIAL INFORMATION

The information contained in this presentation is the confidential and proprietary information of Synopsys. You are not permitted to disseminate or use any of the information provided to you in this presentation outside of Synopsys without prior written authorization.

## IMPORTANT NOTICE

In the event information in this presentation reflects Synopsys' future plans, such plans are as of the date of this presentation and are subject to change. Synopsys is not obligated to update this presentation or develop the products with the features and functionality discussed in this presentation. Additionally, Synopsys' services and products may only be offered and purchased pursuant to an authorized quote and purchase order or a mutually agreed upon written contract with Synopsys.

# Overview

- Introduction

- Motivation

- Optics in Data Centers

- Emergence of AI/ML, Explosion of Data Traffic

- Flattening of Networks for Low Latency, and Aggregation of Homogeneous Resources

- NPO, CPO

- Re-thinking Electrical-Optical Interface

- Optical I/O Roadmap

- Optics as an Enabler to PCIe and UCIe

- "Convergence" of Ethernet, PCle and UCle

- 3D-HI and Impact on the Design Automation

- Multi-Die, System-of-Chips Implications

- Summary

## Acronyms in Order of Appearance

**HPC:** High-Performance Computing

PIC: Photonic Integrated Circuit

AI: Artificial Intelligence

ML: Machine Learning

I/O: Input and Output

NPO: Near-Packaged Optics

**CPO: Co-Packaged Optics**

PCIe: Peripheral Component Interconnect Express

UCIe: Universal Chiplet Interconnect Express

3D-HI: 3D Hybrid Integration

PC: Personal Computer

AR/VR: Augmented/Virtual Reality

5G: 5<sup>th</sup> Generation

LiDAR: Light Detection & Ranging

E-O-E: Electrical, Optical, Electrical

NRZ: Non-Return to Zero

PAM4: 4-level Pulse Amplitude Modulation

QPSK: Quadrature Phase-Shift Keying

HBM: High-Bandwidth Memory

MCM: Multi-Chip Module

TOR, ToR: Top-of-the Rack

DAC: Digital-to-Analog Converter

**GPU: Graphic Processing Unit**

**ISP: Internet Service Providers**

DC: Data Center

DCI: Data Center Interconnect

POD: Not an acronym (modular and scalable unit)

**CPU: Central Processing Unit**

QSFP: Quad Small Form-Factor Pluggable

BGA: Ball Grid Array

OE: Optoelectronic

SERDES: Serializer, De-Serializer

LR: Long Reach

VSR: Very Short Reach

PHY: Physical layer (of the networking model)

**DSP: Digital Signal Processing**

DRV: Driver

TIA: Trans-Impedance Amplifier

PD: Photo-detector

Mod: Modulator, Modulation

# Acronyms in Order of Appearance (Continued)

IC: Integrated Circuit

CXL: Compute Express Link

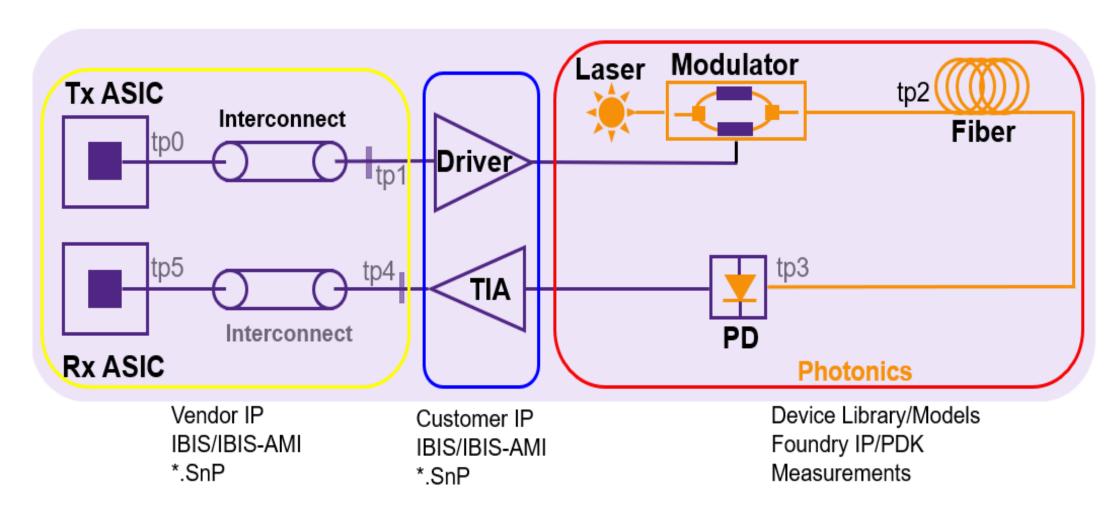

Tx, TX: Transmitter

Rx, RX: Receiver

tp#: Test Point #

IP: Intellectual Property

IBIS: Input/Output Buffer Information Specification

AMI: Algorithmic Modeling Interface

SnP: Data file extension for a Touchstone file

PDK, ADK: Process/Assembly Design Kit

XSR: Extra-short Reach

AFE: Analog Front End

MZM: Mach-Zehnder Modulator

MRM: Micro-Ring Modulator

EAM: Electro-Absorption Modulator

**BW: Bandwidth**

RIN: Relative Intensity Noise

MB/s, GB/s, TB/s: Mega, Giga, Tera bits per second

SIP: Silicon Photonics xPU: Cross-Point Unit

D2D: Die-to-Die

OIF: Optical Internetworking Forum

PCI: Peripheral Component Interface

SIG: Special Interest Group

GbE, TbE: Giga-bit and Tera-bit Ethernet

ZR: Zero-dispersion shifter

LR: Long Range

**EDA: Electronic Design Automation**

SW: Software

Pkg: Package

DDR: Double-Data Rate

InFO: Integrated Fan-Out

RDL: Re-Distribution Layer

KGD: Known Good Die

TCAD: Technology Computer Aided Design

RF: Radio Frequency

EM: Electro-magnetic

PEX: Parasitic Extraction DRC: Design Rule Check

LVS: Layout-versus-Schematic

## Introduction/Motivation

Accelerating PIC Adoption in Established Markets

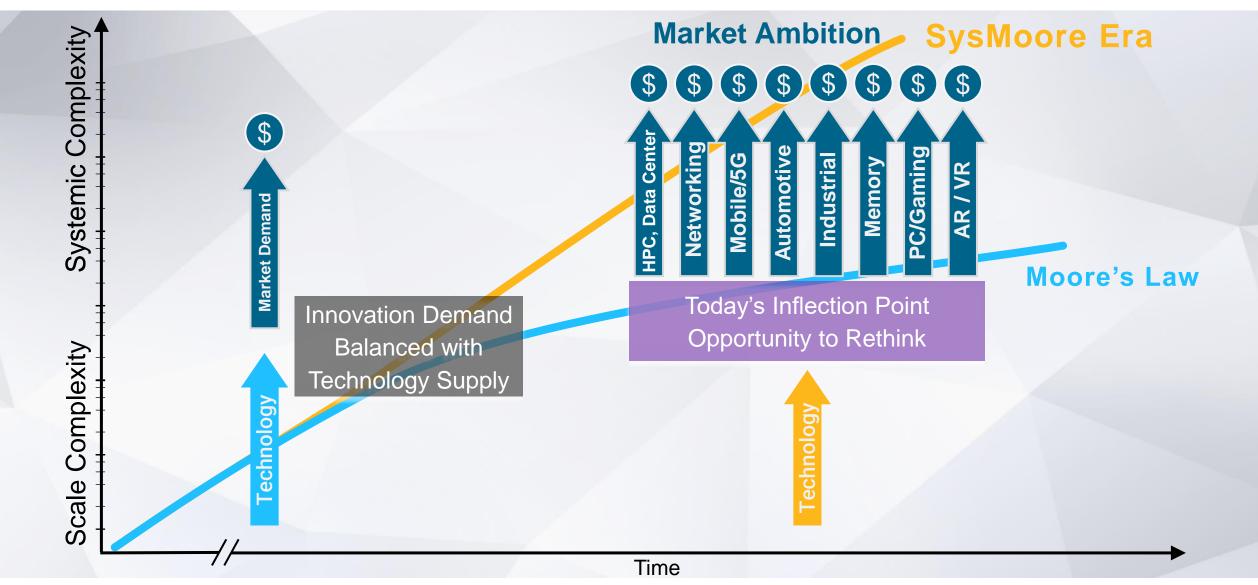

# **Changing Market Dynamics**

# Technology Updates and Future scope

New applications are emerging because

Loss handling is getting more expensive in copper and costly with the data rate growing rapidly

AI/ML demands are growing and requesting different architectures to save power, reduce latency

Different standards are adopting E-O-E interconnect driven by the need for low power and low latency → PCIe over optics, Optical Chiplets, and more

Wearables Consumer LiDAR / Automotive Fiber Optic Gyro Tele & Data Transceivers / Co Packaged Optics Comm **HPC** Optical I/O Photonic Computing / Computing Quantum Computing (AI/ML)

# Opportunities for Optics to go Deeper into the Data Centers

Accelerating PIC Adoption in Established Markets

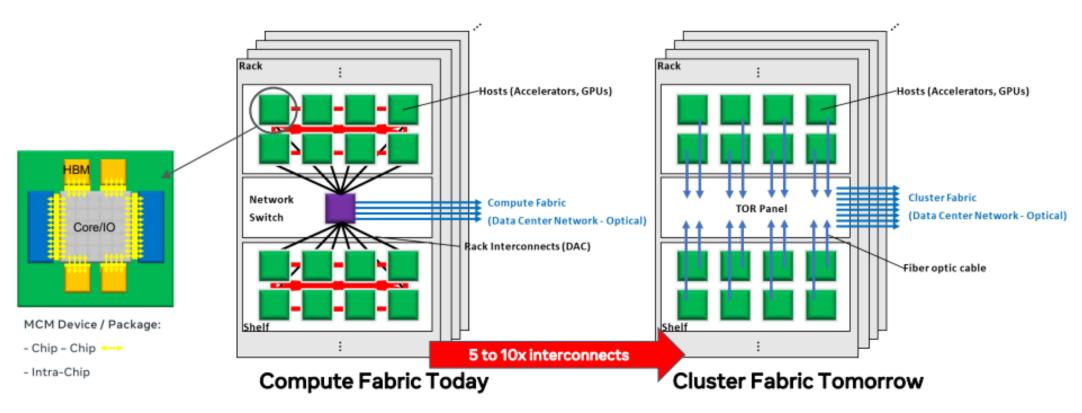

# Interconnect Scaling Challenges

AI/ML growth has led to an increased cluster size and IO demand

Source: Meta

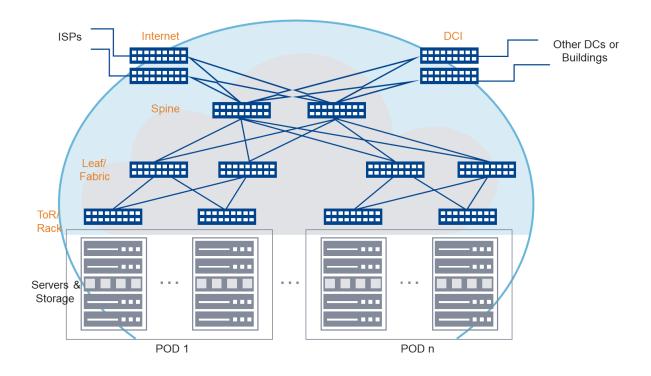

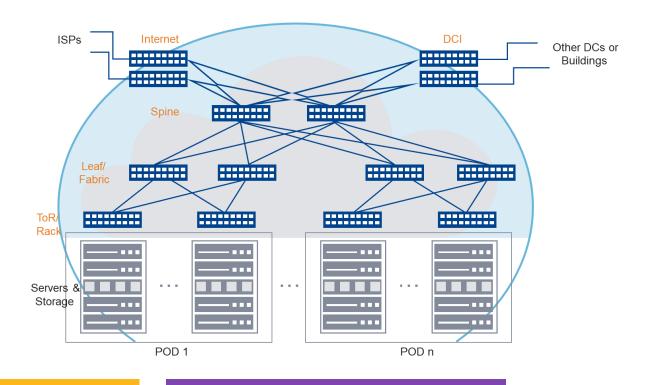

# Main Trends Driving Optics into the Data Center

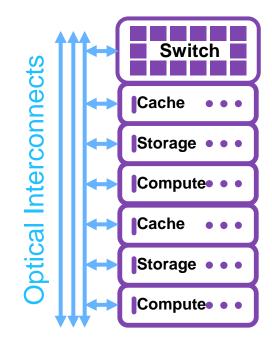

"Fatter" links extending up to 10s of meters within pod efficiently supported with optical interconnects

Explosion of Data Traffic in Data Centers

# Main Trends Driving Optics into the Data Center

Explosion of Data Traffic in Data Centers

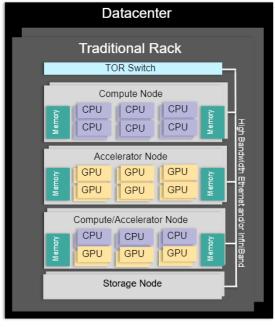

Flattening of Networks for Low Latency

## Main Trends Driving Optics into the Data Center

© Hyperion Research 2023

Explosion of Data Traffic in Data Centers

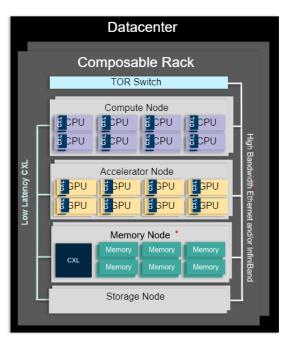

Flattening of Networks for Low Latency Aggregation of Homogeneous Resources in Rack

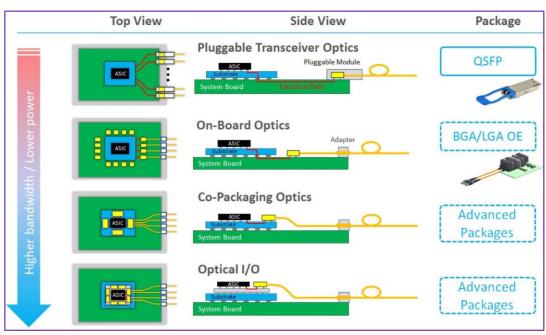

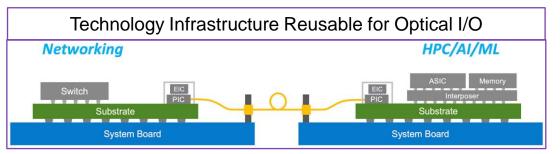

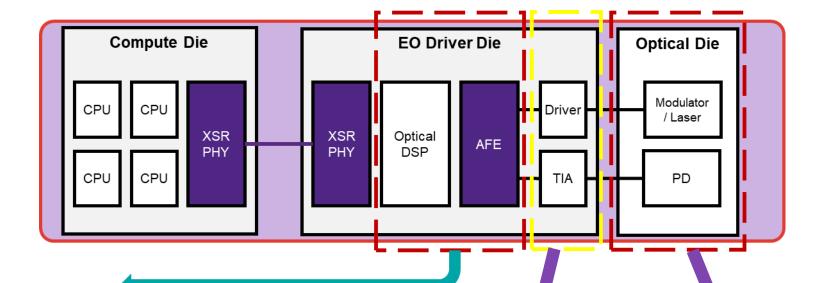

# Optical Datacom Moving to Near- & Co-Packaged Optics

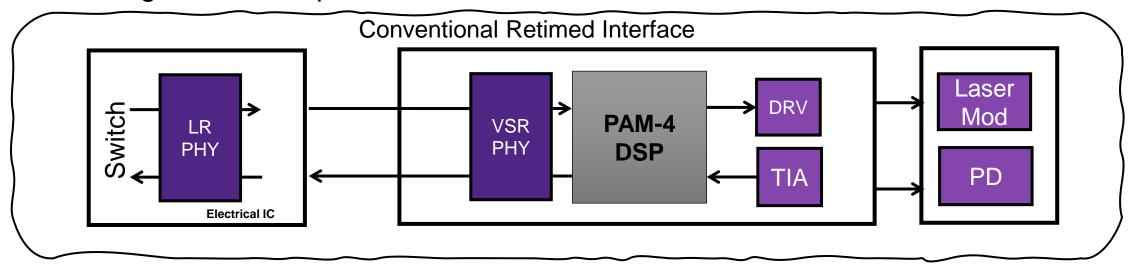

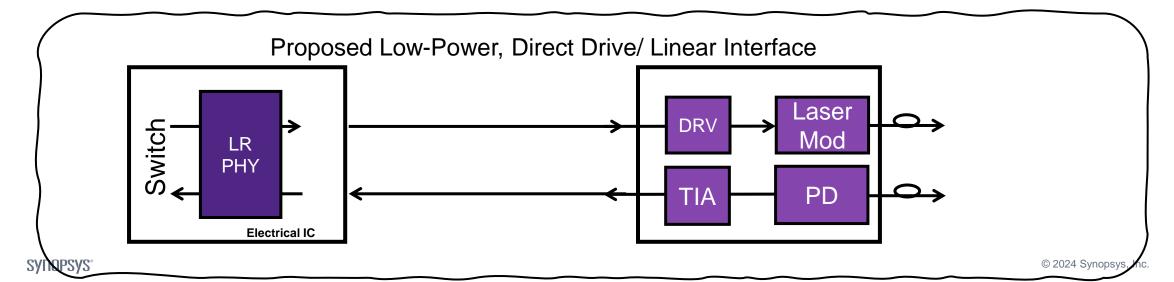

## Re-thinking Electrical-Optical Interface

- Complexity going up

- Proximity of <u>Electronics and Photonics</u>

- From single chip to <u>Multi-Die/Multi-Domain</u> System

- Power density & Temperature sensitivity

- Reliability

- Changing role for SERDES in the system

- → Impact on IP

https://ase.aseglobal.com/en/technology/silicon-photonics

https://ase.aseglobal.com/en/technology/silicon-photonics

# Opportunities for Advances in Electrical-Optical Interface

Accelerating PIC Adoption in Established Markets

# Accelerating PIC Adoption in Established Markets

## Re-thinking Electrical-Optical Interface

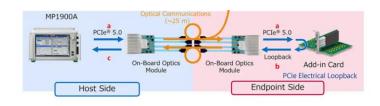

## **Next Generation PCIe**

For Low Power / Low Latency, Disaggregation with Compute Express Link (CXL)

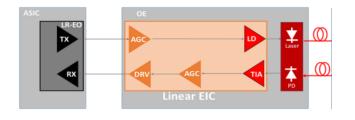

# Photonic Components in an Optical Links

### **Major Components**

- Laser

- Laser Driver

- Modulator (MZM, MRM, EAM)

- Photodiode

- TIA

#### **Fully Electrical**

- High TX equalization capability

- High RX equalization capability

- RX May need nonlinear Equalizer

## **Fully Electrical**

- Linear driver with high amplitude

- Low noise, linear TIAs required

**Electro-Optical Components**

- High BW E-O modulators required

- Laser with Low RIN

- High BW, High sensitivity, and high Responsivity PDs required

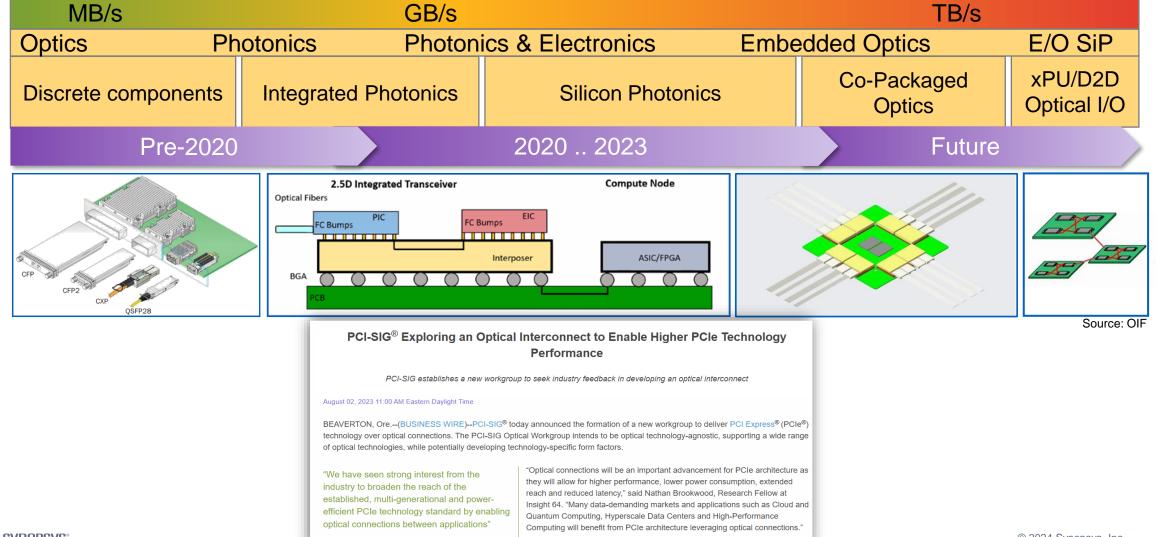

# Optical I/O Technology Roadmap

Tweet this

#### Relentless Innovation

# Opportunities for PIC due to the Pressure on PCIe/UCIe to Deliver

Accelerating PIC Adoption in Established Markets

# More Standards Are Adopting Optics

OIF is Leading the Move; PCI-SIG and UCIe Consortium are Joining

- 112G Linear Optics

- 56G Linear Optics

- 800G ZR

- 800G LR

- New Energy efficient optical interfaces

- Defined UCIe Retimers for off Package Optical interconnect

- Discussions on Optical interface for PCIe interconnects Retimed or Un-retimed

- New workgroup to deliver PCIe technology over optical connection

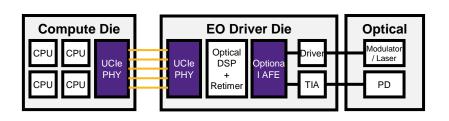

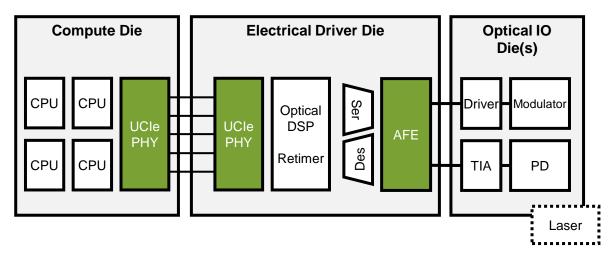

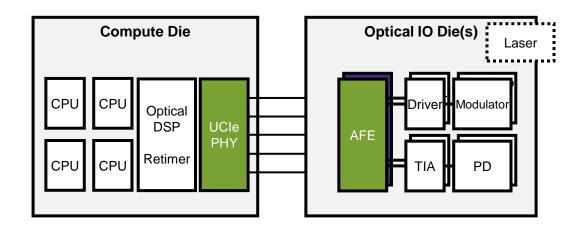

## CPO with D2D UCIe

For Low Power / Low Latency, Dense Networks Within DC

- A three-die implementation with UCle PHY allows true open multi vendor integration

- Laser integration is shown as an option

- Robust interoperability at the cost of slightly higher power

- A two-die implementation with UCIe PHY in allows custom implementation for a reach and vendor

- Laser integration is shown as an option

- Saves power as avoids a stage of interconnect

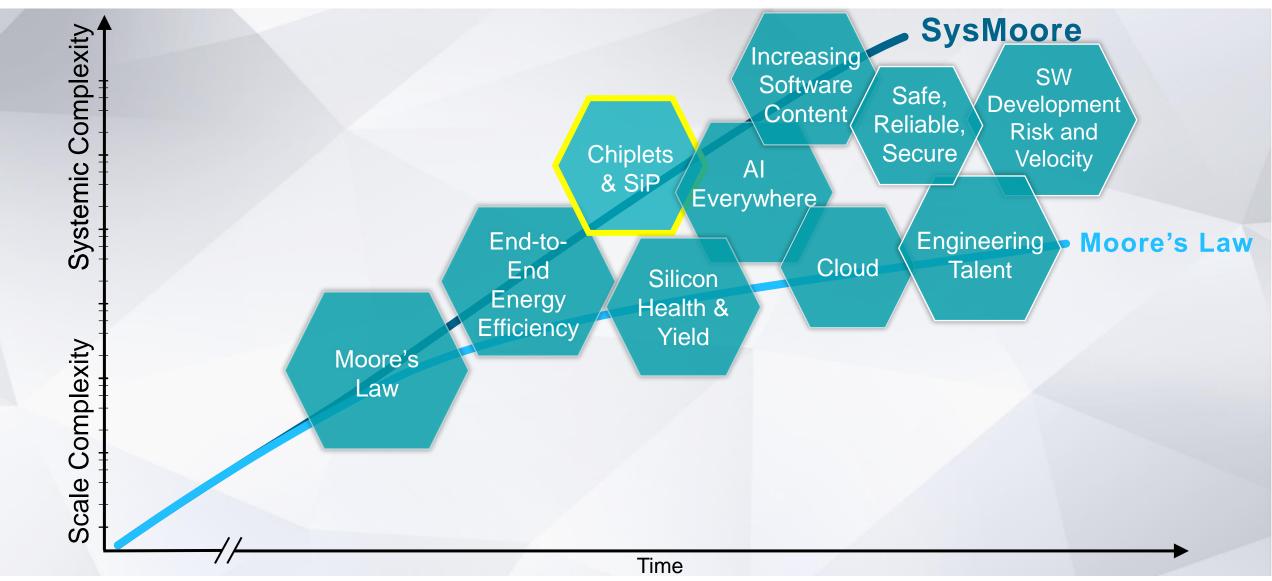

# Opportunities for the EDA Industry

Due to Accelerating PIC Adoption and 3D-HI

# Techonomic Disruptors in SysMoore Era

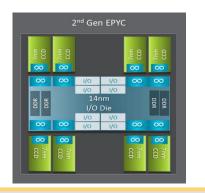

# Multi-Die Systems are Here

#### AMD Epyc Server CPU

- Scale & Disaggregate IO

- 8 Compute Die +

- 1 I/O Die

- Substrate Pkg

## Apple M1 UltraMax CPU

- Scale use case

- 2 Compute Die

- Silicon Interposer Pkg

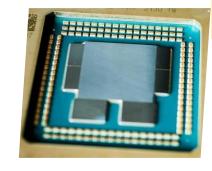

#### Tesla Dojo Training Tile

25 chiplets

packaged in

TSMC's InFO

with 6 RDL

(3 thick for power)

# Amazon Graviton3 Server CPU

- Disaggregate IO

- 1 Compute Die +

- 4 DDR Die + 2 I/O Die

- Substrate Pkg

# Intel Ponte Vecchio Xe-HPC GPU

- Scale & Disaggregate IO

- 16 Compute Die +

- 8 Cache Die + 2 Base Die

- 8 HBM Die + 2 IO Die

- EMIB + Foveros Pkg

# Multi-Die System Design Adds New Complexities

Opportunities for the EDA Industry

## Co-design

- Leveraging EDA tools

- Early modelbased architectural exploration

### Reliable Die-to-Die Connectivity

Include features to meet multi-die system requirements

# Designing at the system level

- System-level validation

- System sign off

- Silicon health during entire operation

# Thermal challenges

- Good thermal and electrical modeling

- Performance per watt becomes critical

### Test challenges

Known good die (KGD) is required

Source: TechSearch International

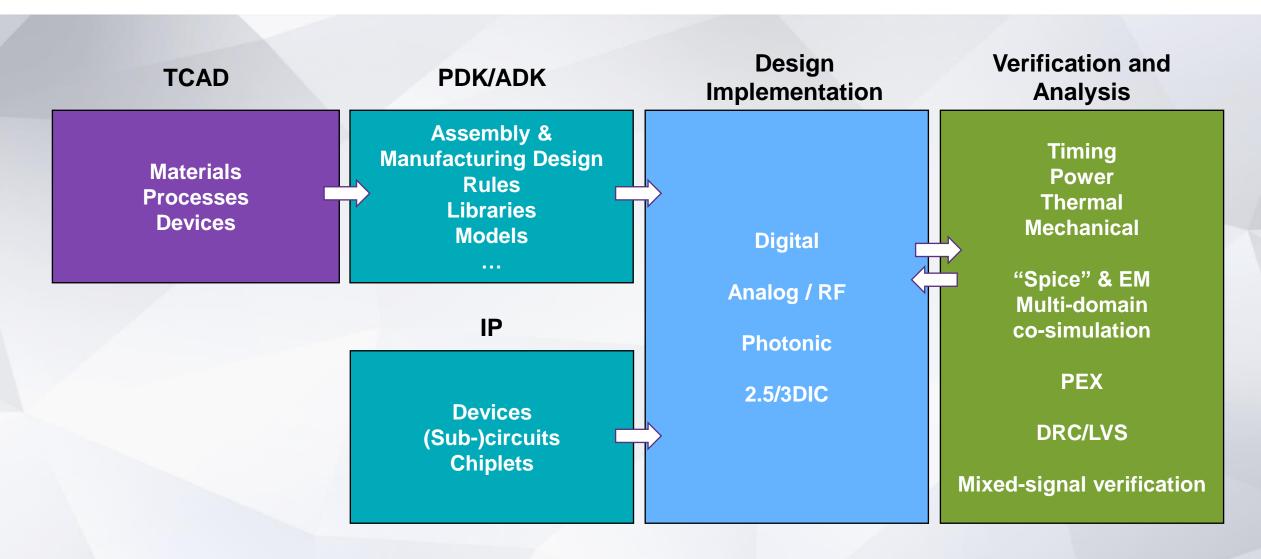

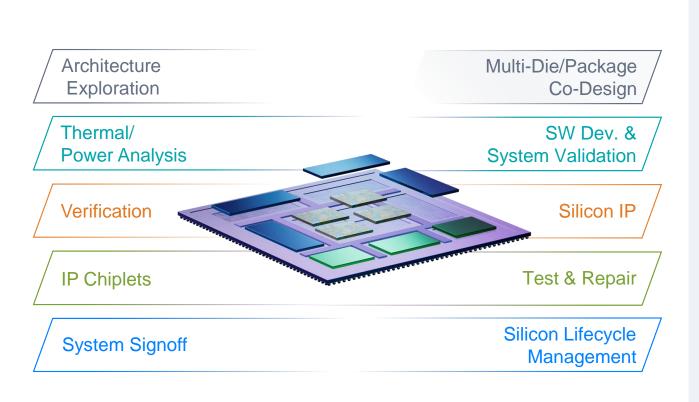

# Multi-Die / Multi-Domain System-of-Chips Design Flow

# Multi-Die System Design

## Critical Design Aspects in 3D Heterogenous Integration

Architecture Exploration

Optimize thermal, power, and performance with early exploration and partitioning

Software Dev. & Validation

Rapid software development and validation with high-capacity emulation & prototyping

Design Implementation Efficient die/package co-design with unified exploration-to-signoff platform and robust IP

Manufacturing & Reliability

Improve health, security and reliability with holistic test and lifecycle management solutions

SYNOPSYS<sup>®</sup>

# Thank You

# **SYNOPSYS®**