## Silicon MOSFETs and IGBTs: evolving for the future

Antonino Gaito Power Transistor sub-Group Strategic Marketing Manager STMicroelectronics

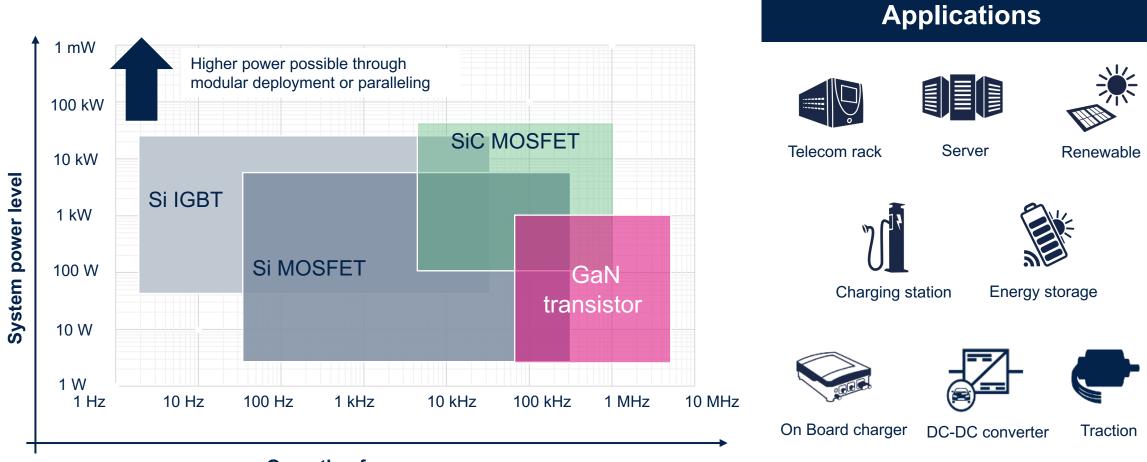

## Power transistor technologies

**Operating frequency**

## Silicon MOSFET: From planar toward new structures

## A power MOSFET operates like a switch

#### Power MOSFET: key player in all applications handling power

Main parameters impacting performance

- $\mathbf{R}_{DS(on)}$  (On-state resistance) [ $\Omega$ ]

- **Q**<sub>G</sub> (Total gate charge) [nC]

- Package

- Breakdown voltage, BVDSS

- Threshold voltage, Vth

- dv/dt capability, output capacitance, more...

R<sub>DS(on)</sub> impacts conduction losses

Gate charge Qg impacts switching losses

Package impacts power density

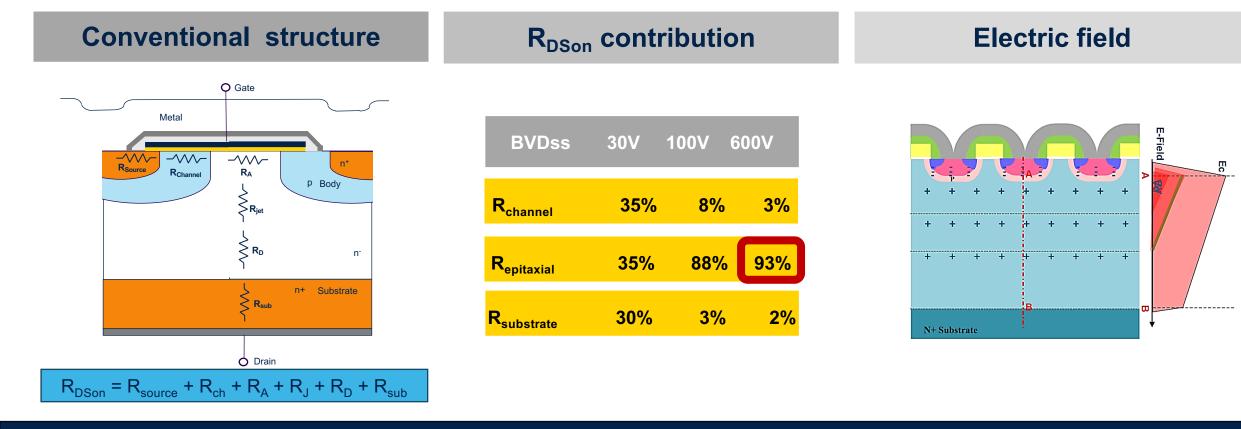

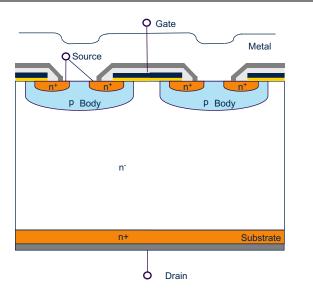

#### Planar MOSFET

- R<sub>DSon</sub> is due mainly to the epi-region for high voltage MOSFETs

- The breakdown voltage is determined by the epitaxial layer (drift layer) doping concentration and its thickness

## **MOSFET** evolution

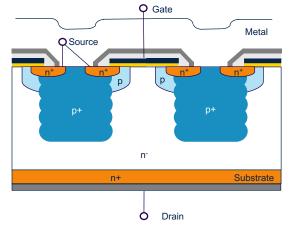

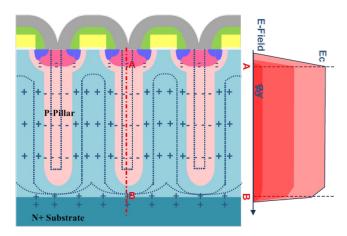

#### **Super-junction**

- Better control of the dynamic behavior ٠

- Improved performance like lower conduction and ٠ switching loss

- Significant Rth reduction due to very thin die ٠

#### Planar

- Thermal performance (Rth) ٠

- Low electromagnetic effects ٠

- **Extended SOA** ٠

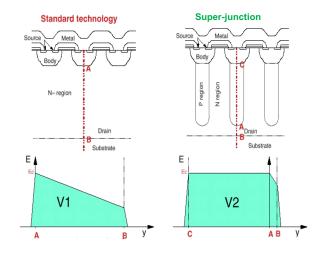

## From planar to superjunction structure

#### Comparison @ same BVdss

| Parameter          | Planar Multidrain               |                                                     |

|--------------------|---------------------------------|-----------------------------------------------------|

| Drift doping layer |                                 | <b>Higher</b><br>Increasing dopant<br>concentration |

| R <sub>DSon</sub>  | Related to Epi<br>layer         | <b>Lower</b><br>Epi layer reduced                   |

| Electrical Field   | Variable<br>During the n region | Higher<br>Increased by column structure             |

$$V(x) = \int E(x) dx$$

| Poisson's Law |                   |                       |                |

|---------------|-------------------|-----------------------|----------------|

| $d^2V$        | dE                | Q(x)                  | $qN_A$         |

| $dx^2 = -$    | $\frac{dx}{dx} =$ | = =<br>ε <sub>s</sub> | ε <sub>s</sub> |

#### **Benefits**

- Higher current density

- Lower Zth

- Suitable for low thickness packages

#### Main features

- Very low R<sub>DS(on)</sub> per area

- Suitable for hard-switching topologies

- Best choice for resonant

high power density systems

- Reducing switching energy losses

- Reducing switching time

- Increasing switching frequency

- Reduced BVdss spread <70V</li>

- Reduced Vth spread <1V

- Higher reliability

- Static dv/dt up to 120V/ns

- Dynamic dv/dt up to 50V/ns

- Dynamic dv/dt up to 120V/ns

## **MOSFET** evolution

#### Active area: cell structure comparison

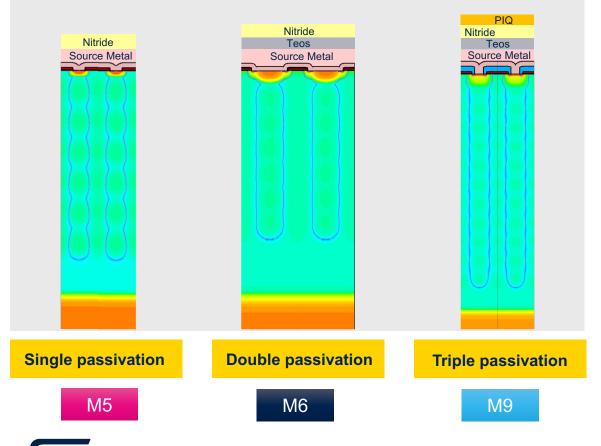

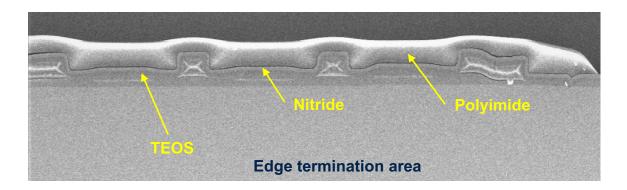

#### **Passivation layers optimization**

- Nitride is an excellent and common passivation layer

- **Teos** layer to reduce Nitride stress

- Extra **polymide** layer (organic polymer that exhibits excellent mechanical properties and electrical insulation) to reduce the mechanical stress coming from BE processes

life.augmented

Note: **MDmesh<sup>™</sup> Mx** are the proprietary technologies of STMicroelectronics

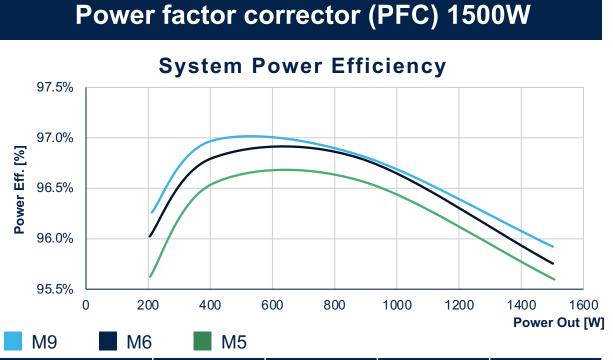

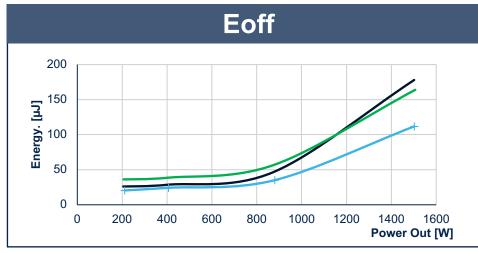

## Application test and analysis

| Device    | BVdss<br>[V] @ 1mA | Vth<br>[V] @ 250uA | R <sub>DS(on)Max</sub><br>[mΩ]* | Qg<br>[nC] |

|-----------|--------------------|--------------------|---------------------------------|------------|

| MDmesh M9 | 650                | 3.7                | 45                              | 80         |

| MDmesh M6 | 600                | 4                  | 41                              | 106        |

| MDmesh M5 | 650                | 4                  | 45                              | 143        |

life.augmented

New technology maximizes system efficiency and thermal performances

## What is next for superjunction?

#

Multidrain approach

Colum by multi epy/implantation and diffusion

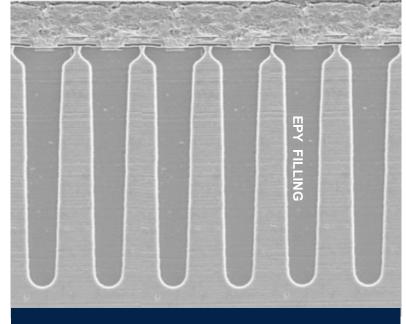

From multi-epitaxy to "dig & fill" approach

#### Trench approach

Column by single epy etch and trench filling

- Reduced mask levels

- Single epitaxy

- No thermal process for column formation

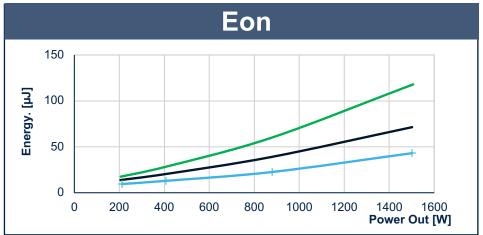

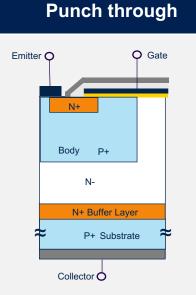

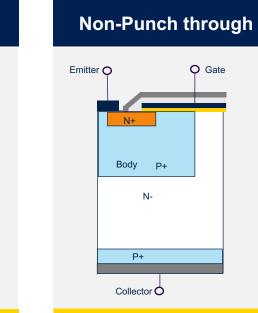

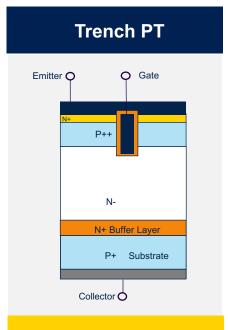

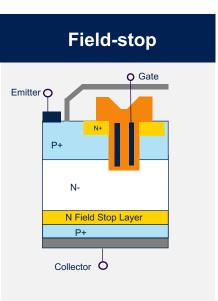

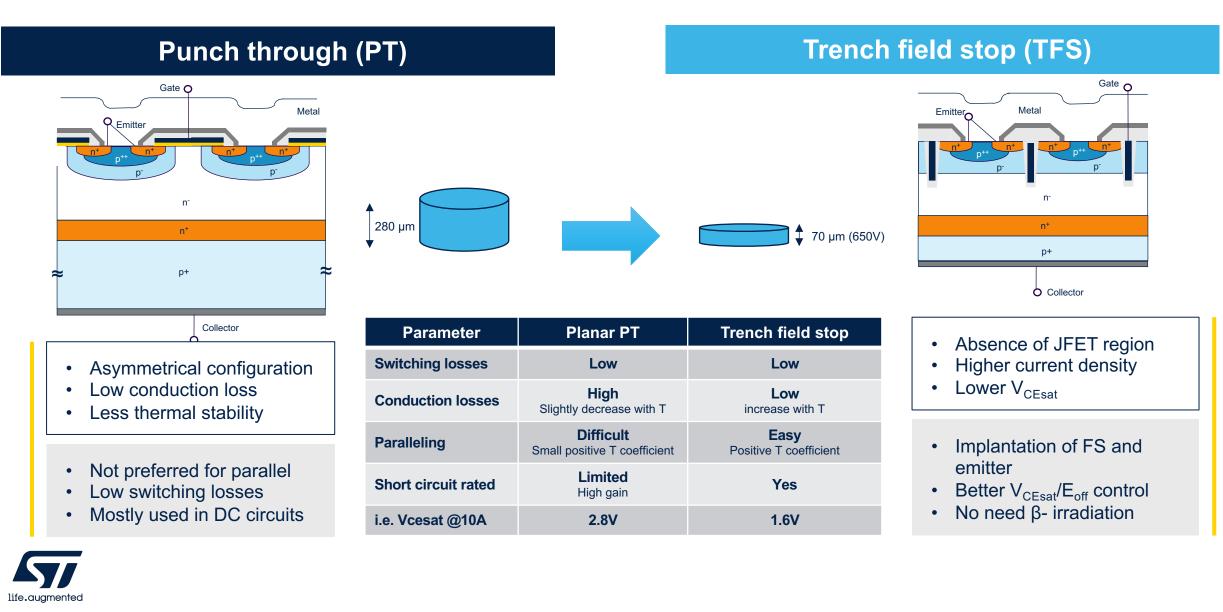

## IGBT: Evolution of a technology

## IGBT technology

- First IGBT structure

- Faster, but higher V<sub>CEsat</sub>

- Large E<sub>off</sub>

- Thinner substrate

- Lower thermal resistance,

- Lower E<sub>off</sub>

- Vertical Gate

- Optimized channel design

- Lower V<sub>CEsat</sub>

- Higher current

density

- no tail current

- Reduced switching losses

- Decreased V<sub>CEsat</sub>

- Thinner n-drift

region

- Lower V<sub>CEsat</sub>

- N+ layer removes

JFET resistance

- Carried stored layer fastens turnon switching ability

## **IGBT** evolution

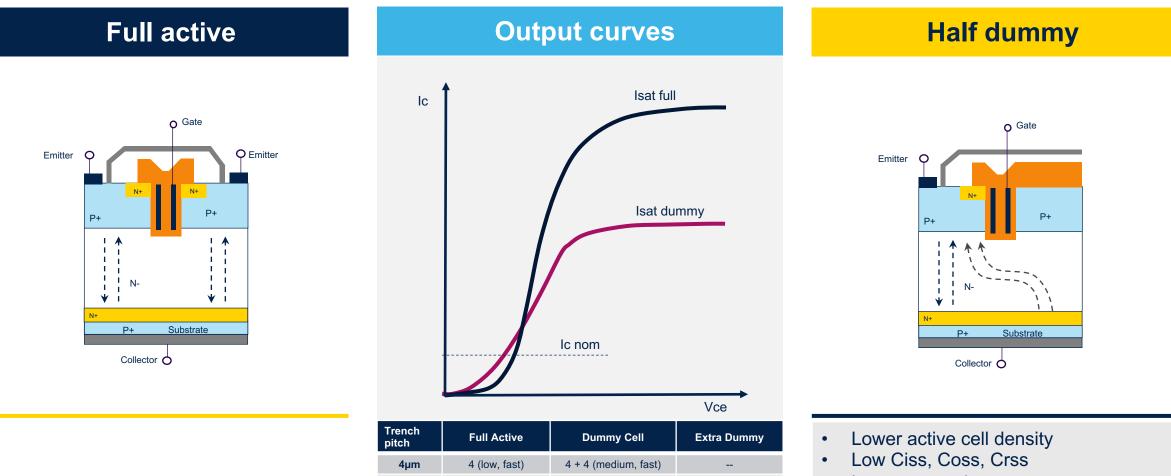

## Trench layout strategy

8 + 8 (medium, fast,

SC rated)

8µm

8 (medium, fast)

8 + 16 (medium,

fast, strong SC

rated

Lower saturation current

• Improved Tsc

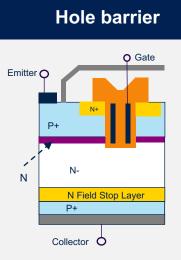

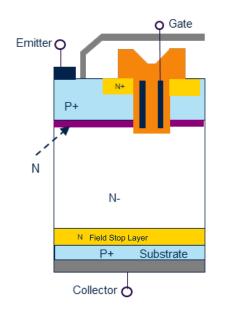

## What's next in Trench Field Stop?

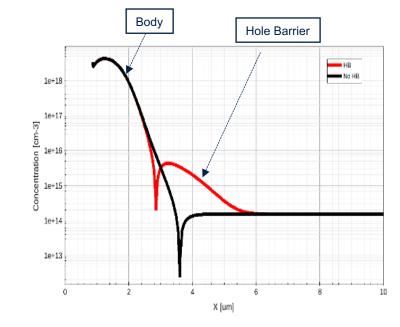

#### **Hole Barrier Structure**

- Process Option

- Additional Mask

- Additional Implant Phosphorus

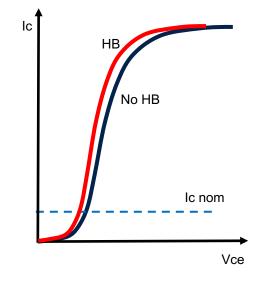

- New vertical profile with additional N-type layer that enhances the majority carriers and so improving the ON state losses

#### Benefit

lower Vcesat ~ 180mV

#### Warning

- Vth lowering to be retuned

- BVces lowering

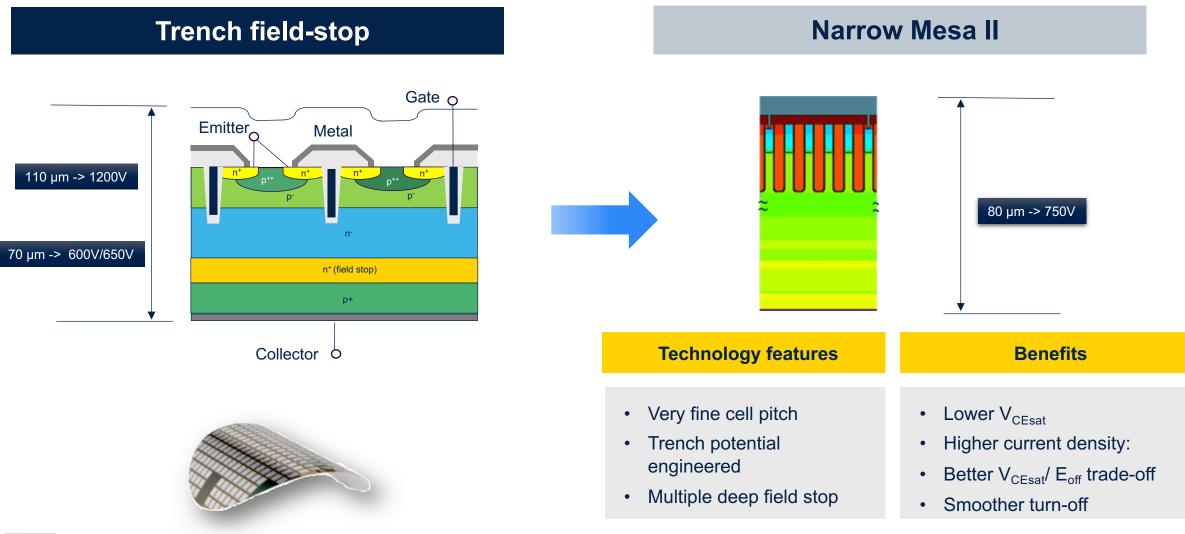

#### Narrow Mesa II

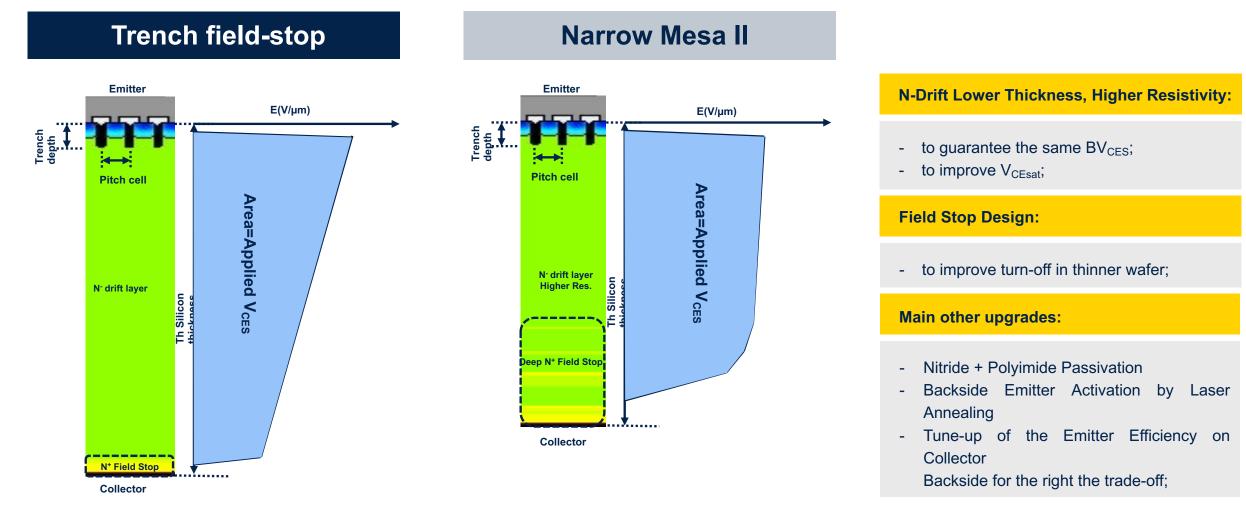

## Main features to improve V<sub>CEsat</sub> and Turn off

## Static electrical improvements

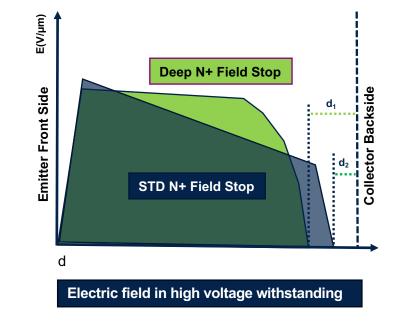

#### **Electrical field: Vertical profile**

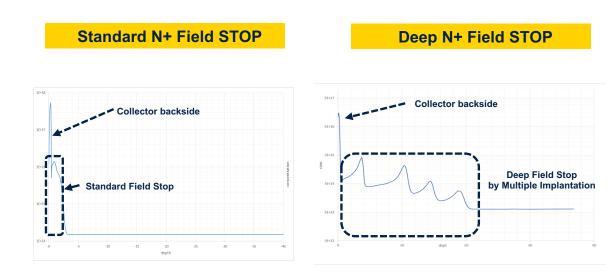

#### Deep Field Stop Layer;

- To gradually block the electric field near the collector side;

- To reduce V<sub>CE</sub> peak at turn-off when "reducing the wafer thickness";

**Narrow Mesa II**

- Multiple field-stop profile shows better resolution of field slope-down to have more robust devices

- Higher efficiency voltage withstanding

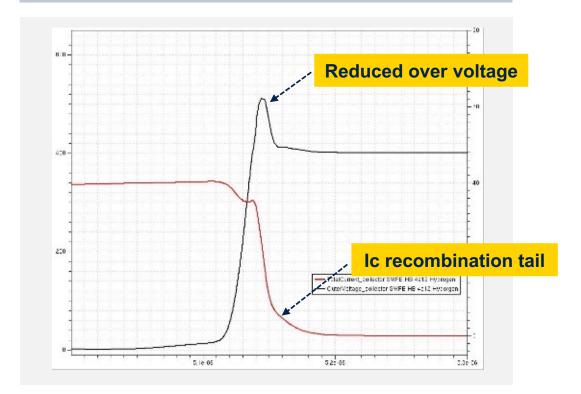

#### Dynamic electrical improvements Turn OFF simulation

# Abrupt Ic fall due to carrier wipe-out by very high bulk electric field

51e-06

5.2e-06

**Standard field stop profile**

#### **Multiple field stop profile**

Multiple field stop design profile technique is used to control the carrier's lifetime improving performance by reducing overvoltage during switching events

#### Takeaways

- Silicon technologies span an extensive market, from industrial to automotive sectors

- The wide product portfolio targets from low to high power range and from low to high frequency operation

- New structures and concepts allow to take up new challenges

- New technologies are one of the key contributors for the green economy

20

## Our technology starts with You

© STMicroelectronics - All rights reserved. ST logo is a trademark or a registered trademark of STMicroelectronics International NV or its affiliates in the EU and/or other countries. For additional information about ST trademarks, please refer to <u>www.st.com/trademarks</u>. All other product or service names are the property of their respective owners.