## What is driving the silicon photonics market?

Yole Dévelopment Report November 2023, PIC dies revenue growth

- Other applications may emerge and drive the technology but ...

- ...today, Datacom / Telecom drives wafer demand towards 2028

- ...tomorrow, AI-driven Datacom I/O & CPO will emerge and drive by 2030-2032

imec

2

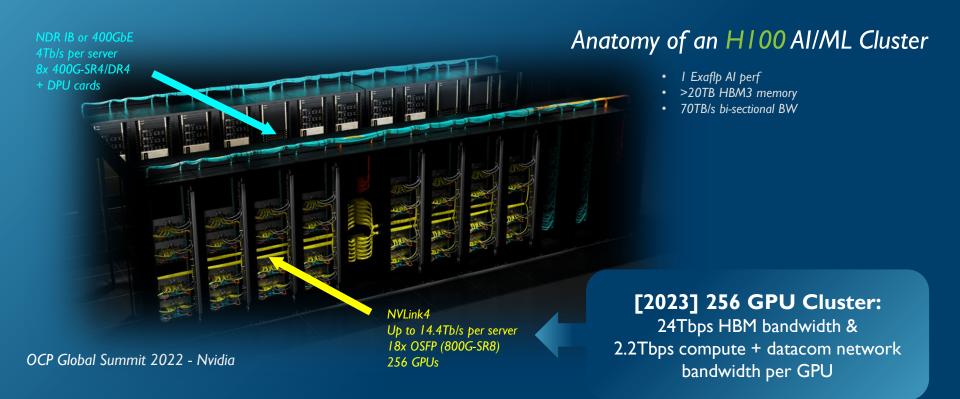

# Optical interconnects in AI/ML compute clusters

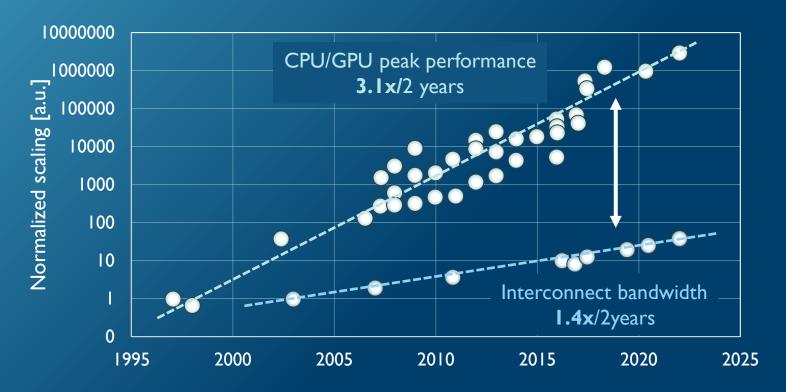

# Interconnect Bandwidth lagging behind Compute Capability

Amir Gholami, et. Al. "Al and Memory Wall", https://medium.com/riselab/ai-and-memory-wall-2cb4265cb0b8

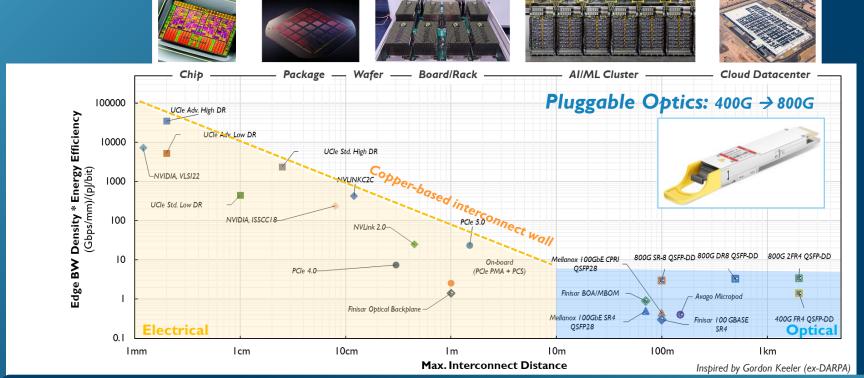

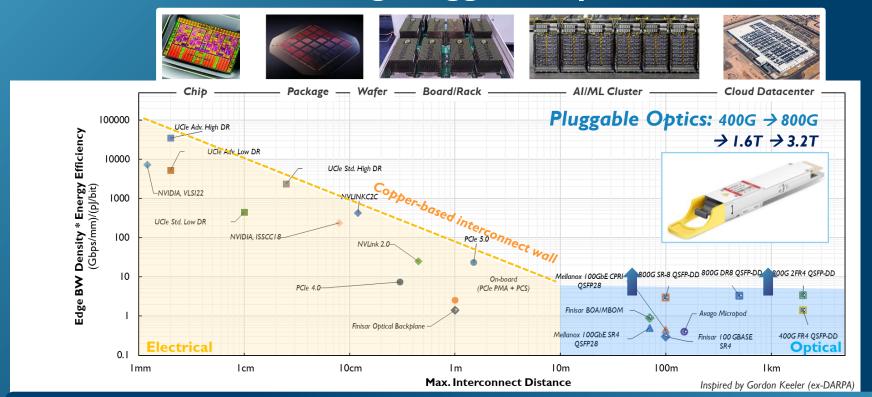

## Interconnect Landscape: Copper vs. Optical

Pluggable Optics are the only option for interconnects beyond Im, but have 2-4x orders worse interconnect performance than board- or chip-level Copper

unec

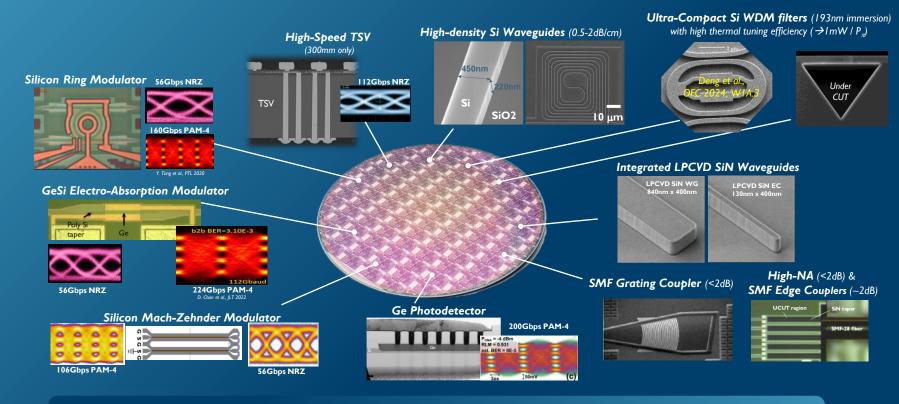

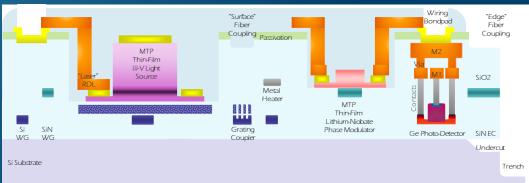

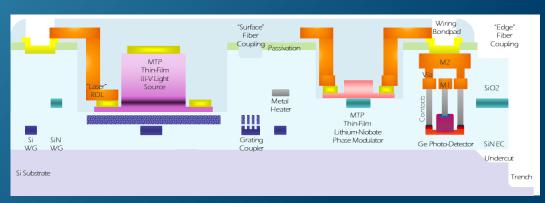

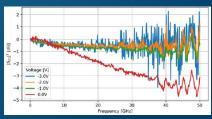

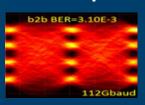

# iSiPP: imec's Silicon Photonics Technology up to 200Gbps/lane

State-of-the-Art Silicon Photonics Platform enabling next-generation 800G and 1.6T Pluggable Optics

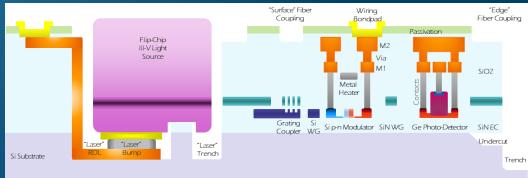

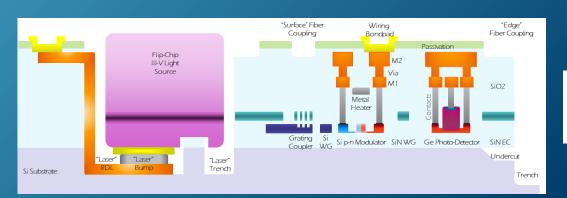

# **Extending iSiPP:** Example #1 - Integrating Light Sources

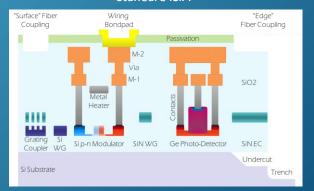

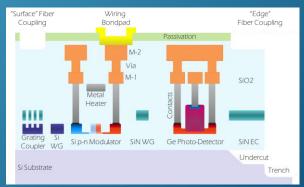

Standard iSiPP

iSiPP with flip-chip bonded III-V laser

+

#### Flip-Chip Bonding (FC)

Sequential bonding of III-V Lasers or Amplifiers with <500nm alignment accuracy

Joint Development partners

ASM 🛞 AMICRA

https://ieeexplore.ieee.org/abstract/document/9956863

Adding High-Power, Flip-Chipped III-V Lasers to the Si Photonics toolbox

# Extending iSiPP: Example #2 - scaling towards 400Gbps/lane

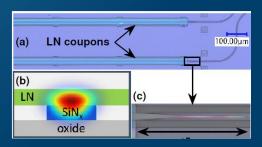

#### iSiPP with Micro-Transfer Printing

#### **Micro-Transfer Printing (MTP)**

Semi-collective bonding of non-Si thin-film devices with <500nm alignment accuracy

T. Vanackere, et al., CLEO 2023

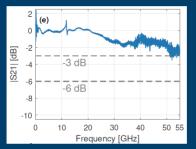

**MTP'ed LNTF** modulators. Early prototype with >55GHz bandwidth

Adding 100GHz Lithium-Niobate Modulators to the Si Photonics toolbox

# European Consortia Driving Silicon Photonics Hybridization Supply Chain

## **Scaling Pluggable Optics**

Hybridized SiPho technology will enable Pluggable Optics at 1.6T and 3.2T

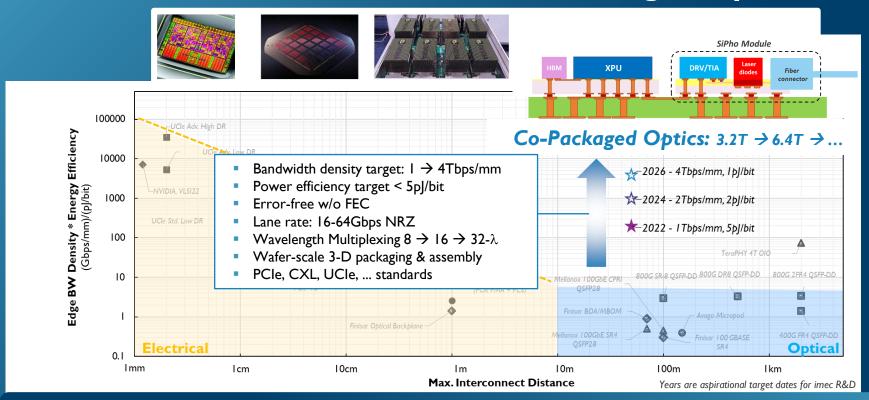

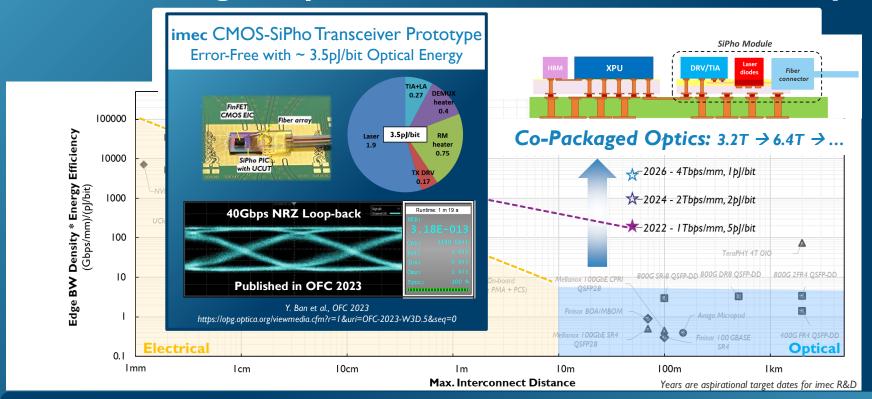

## Great, but what's next? Enter Co-Packaged Optics

Co-Packaged Optics is needed for Disruptive Scaling beyond Pluggable Optics

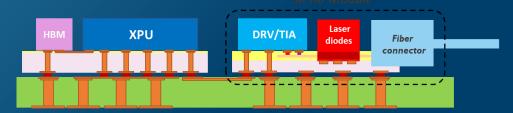

# 3D-enabled co-packaged optics

|                                    | Scaled µbumps<br>(WLUF) | Embedded µbumps  | Die-to-Wafer<br>Hybrid Bonding | Wafer-to-Wafer<br>Hybrid bonding |

|------------------------------------|-------------------------|------------------|--------------------------------|----------------------------------|

| Pitch                              | 50μm → 20μm             | 40μm → 5μm (3μm) | 20µm → 3µm (2µm)               | 3μm → 0.5μm (0.4μm)              |

| Die-to-die gap                     | I2µm                    | 4µm              | ~0µm                           | ~0µm                             |

| Cross-section                      |                         |                  |                                | IIIIII                           |

| Interface parasitic<br>Capacitance | ~60fF → ~15fF           | ~40fF → ~2fF     | ~10fF → ~1fF                   | ~2fF → <1fF                      |

3D/TSV enabled Co-Packaged Optics

Energy efficiency scaling with 3D bonding technology scaling with low capacitance

# Co-Packaged Optics for ultra-low Power and Latency

Co-Packaged Optics is needed for Disruptive Scaling beyond Pluggable Optics

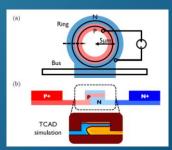

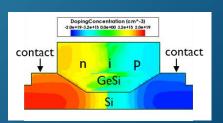

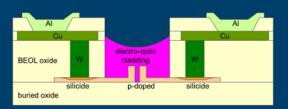

## What **Modulator** For CPO & Interposer?

#### **Established Si-based Options**

#### Micro Ring/Disk Modulator

### 160Gbps

Y. Tong et al., PTL 2020

#### **Ge/Si Electro-Absorption Modulator**

## 224Gbps

D. Chan et al., JLT 2022

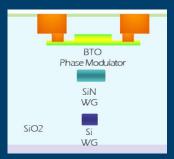

#### **Alternative Materials Options**

#### Silicon-Organic

Courtesy W. Bogaerts

#### **Pockels**

Courtesy F. Ferraro

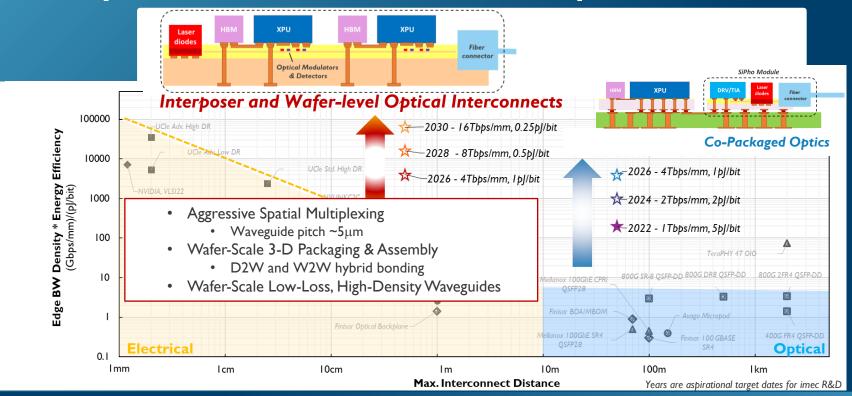

## Optical Interconnects on the Interposer and Wafer

Optical Interposers for Chip-to-chip and Off-Package Interconnects with the performance of short-reach Copper, at 100x Reach

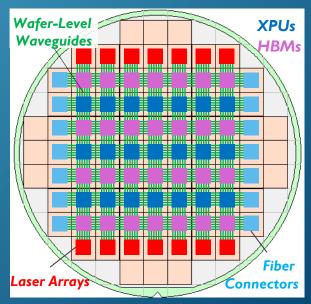

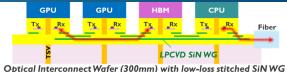

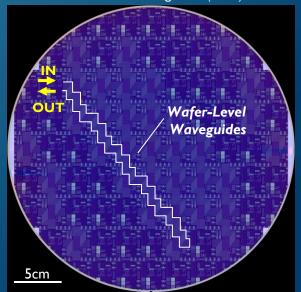

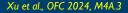

## Vision: Towards Optically Interconnected Systems-on-Wafer

Optically Interconnected System-on-Wafer

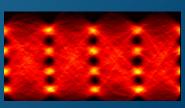

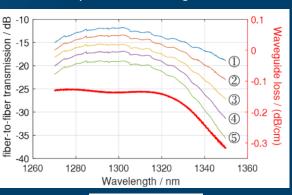

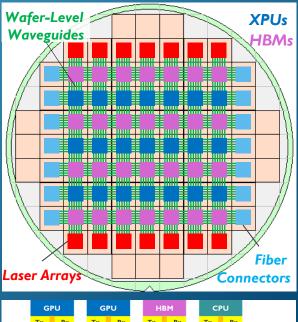

First 300mm wafer-level reticle-stitched interconnect waveguides (imec)

Measured Wafer-level Loop-back SiN Waveguides

300-mm wafer-level waveguides up to 56cm long, with low all-in propagation loss (0.15dB/cm)

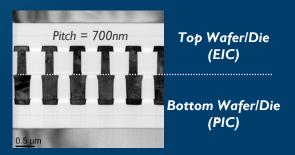

# Vision: Towards Optically Interconnected Systems-on-Wafer

Optically Interconnected System-on-Wafer

GPU GPU HBM CPU

Tx Rx Tx Rx Fiber

LPCVD SiN WG

Optical Interconnect Wafer (300mm) with low-loss stitched SiN WG

300mm wafer populated with Collective Die-To-Wafer Cu-Dielectric Hybrid Bonding With Electrical & Optical Interfaces

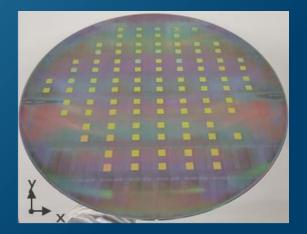

Measured Wafer-level

Distribution of Die-To-wafer

Transition Loss

**Die-to-Wafer Transition Loss < 0.5dB**

## **Takeaways**

- AI/ML and HPC Systems are driving aggressive growth in optical networking

- State-of-the-Art Silicon Photonics enables 800G and first-gen 1.6T pluggable optics

- Upcoming Hybridized Silicon Photonics platforms will enable pluggable modules up to 3.2T

- Co-Packaged Optics aims at a further 100x scaling of optical interconnect performance

- Highly efficient and compact modulators will be required

- Optical Interconnects are likely to replace long-range Cu interconnects at the Interposer and Wafer level, Leveraging 3D-enabled Silicon Photonics

Thank You

Philippe Absil

Acknowledgments

Joris Van Campenhout and the imec silicon photonics team