#### **AIM Photonics**

### AIM Photonics Foundry providing Co-Process and Co-Development to Address Challenges in Photonic Integrated Circuit (PIC) Packaging

Presented by David Harame, COO AIM Photonics

April 16, 2024 12:00-12:15 PM, Brussels, Belgium PIC Packaging: Securing Optimal Integration and Performance

#### AIM Photonics – A US Department of Defense Manufacturing Innovation Institute

Advance integrated photonic circuit and Make the technology available Create an adaptive integrated packaging **manufacturing** technology photonic circuit workforce

AIM provides an <u>accessible</u> best in class state-of-the-art 300mm Photonic Integrated Circuit (PIC) MPW, Heterogeneous-Integration (HI), Interposers, and Test, Assembly, & Packaging (TAP) capabilities and services. We provide end-to-end photonics and advanced packaging solutions.

**NYCREATES** Albany NanoTech Facility

- AIM uses the Albany NanoTech 300mm Facility with (>130K square feet of class-1 clean room)

- AIM also has the Rochester Test Assembly and Packaging (TAP) facility (12K square feet of class-1000 clean room)

#### AIM Photonics TAP facility

AIM Photonics Foundry providing Co-Process and Co-Development to Address Challenges in Photonic Integrated Circuit (PIC) Packaging

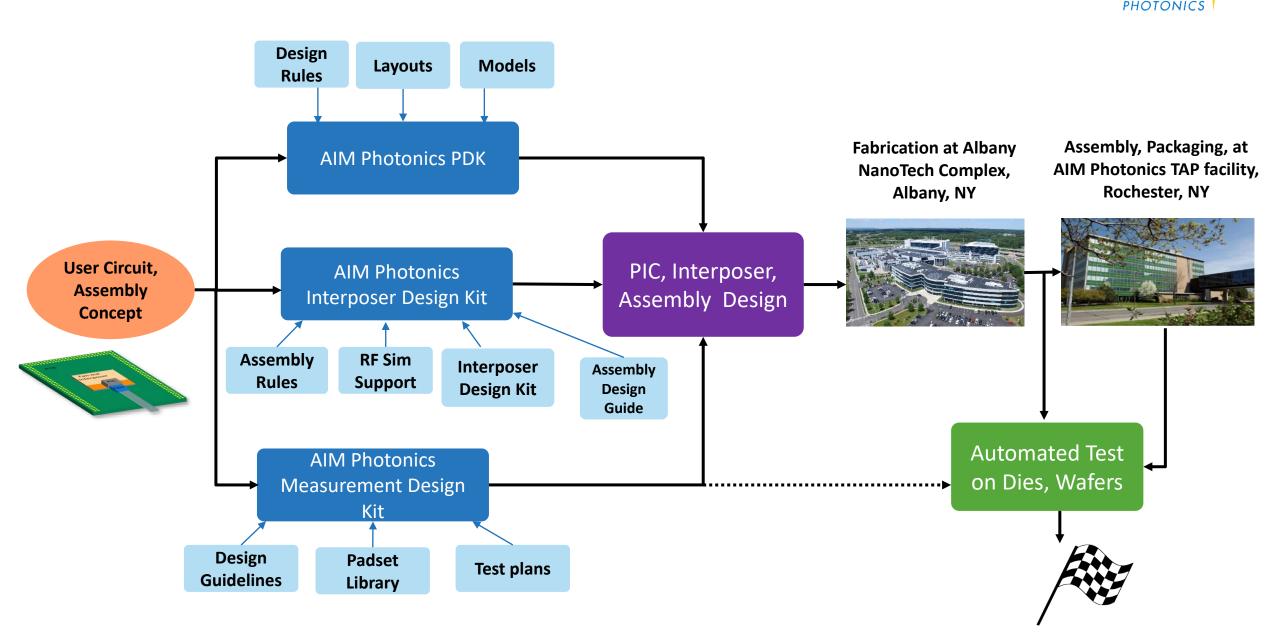

#### AIM Photonics PIC and Packaging Foundry enables co-design

- Co-process Co-design is critically important for low cost low loss integrated photonic packaging

- It is important to leverage already existing electronic packaging assembly processes and tools in copackaged optics designs.

- AIM has both the PIC side and the packaging side which enables co-design and an end to end "accessible" flow

- Innovation requires facilities with access to basic electronic and photonic packaging processes to try out new solutions

- Standardization is key for the industry to develop low cost solutions

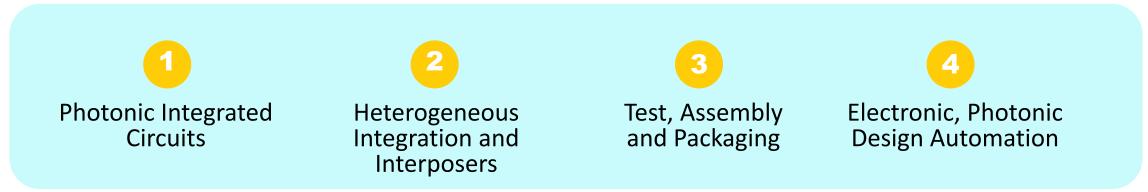

#### **AIM Photonics Core Areas**

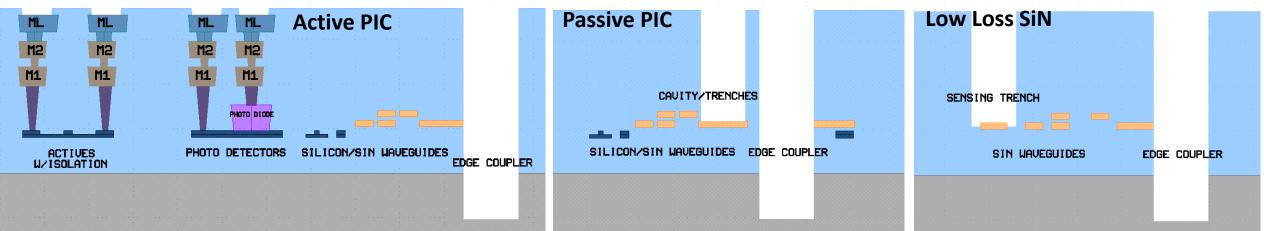

## AIM Photonics Production PIC MPW Technology Offerings

• AIM has a regular schedule of its best in class, mature 300mm PIC and Interposer MPW runs.

https://www.aimphotonics.com/mpw **Electronic Interposers** AIM has quarterly MPW release schedule MЭ MЭ MЭ M2 Best in class 300mm technology M1 M1 M1 performance UM SUBSTRATE 100 Accessible technologies with customization Fastest 300mm MPW turnaround time Active and Passive PIC, Sensors low loss SiN, RDL RDL RDL and Electronic Interposers

٠

٠

٠

٠

٠

RDL

MЭ

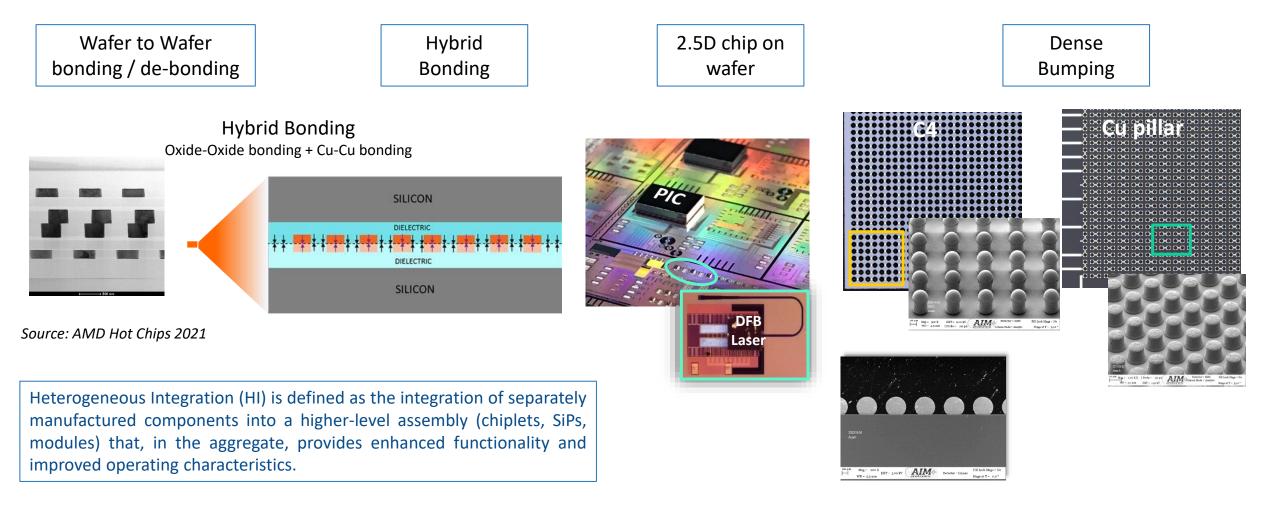

#### AIM Photonics' 300mm Wafer Level Heterogeneous Integration

These are AIM Photonics' processes running in the 300mm wafer HI center in Albany NY. AIM will do custom Heterogeneous Integration services for complex Co-Packaged optics.

**ØNY**CREATES

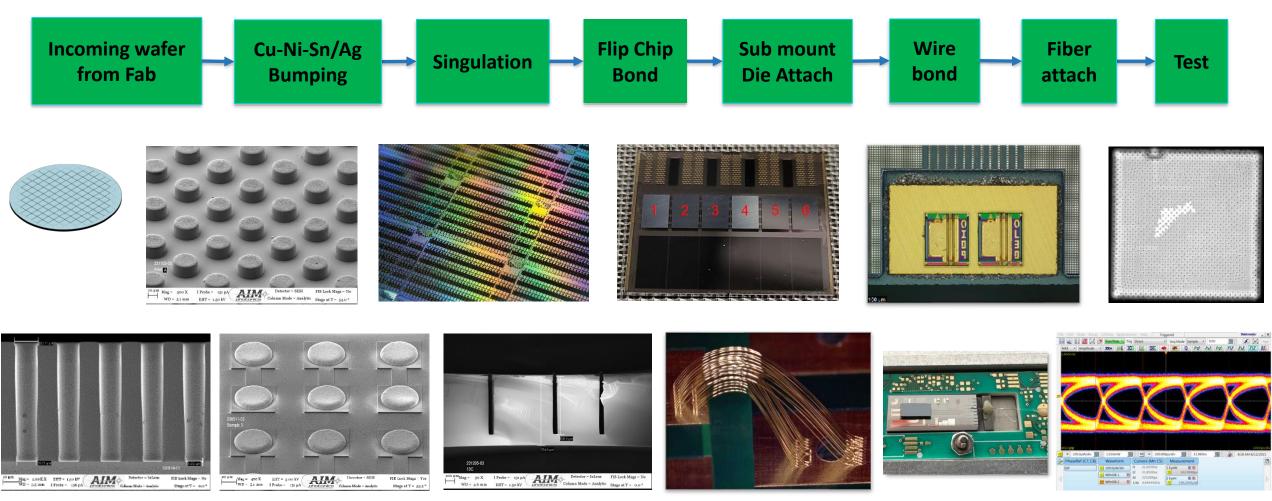

# Existing and enabling processes at TAP

• The existing toolset at TAP is capable many types of 3D assembly builds from 300mm wafer bumping to chip-level thermocompression bonding, fiber attach, metrology and test.

AIM Photonics Foundry providing Co-Process and Co-Development to Address Challenges in Photonic Integrated Circuit (PIC) Packaging

**ON YORE**

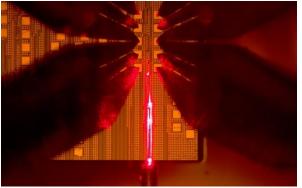

### Techniques to attach a laser to a silicon PIC

• On-chip light sources are becoming more attractive due to tight integration with the PIC and low coupling losses

**ØNY**CREATES

- Utilize Known-Good-Die (KGD) from commercial vendors

- Leverage existing infrastructure and expertise

- For lower volumes and to maximize yield, flip-chip laser integration is preferred

| Conventional off-chip laser | Gain 🗧 Kriso Off-chip |                         |                          |                      |                      | •                           |                                                | •                             |

|-----------------------------|-----------------------|-------------------------|--------------------------|----------------------|----------------------|-----------------------------|------------------------------------------------|-------------------------------|

| FSO                         | al FSO                | Integration             | Conventional<br>off-chip | Off-chip with<br>FSO | Off-chip with<br>PWB | 2.5D HI (flip-<br>chip/µTP) | Hybrid III-V<br>coupon (Direct<br>bonding/μTP) | Monolithic<br>(heteroepitaxy) |

|                             |                       | Coupling Loss           | >2dB                     | >2dB                 | >2dB                 | 1dB                         | 1dB                                            | Few dB                        |

| Off chip with Photonic Wire | IVIONOIITNIC          | Output Power            | High                     | High                 | High                 | Medium                      | Medium                                         | Low                           |

| Bond (PWB).                 |                       | Polarization<br>Control | Needed                   | Needed               | No Need              | No Need                     | No Need                                        | No Need                       |

|                             |                       | Thermal<br>Management   | Easy                     | Easy                 | Easy                 | Medium-<br>Difficult        | Difficult                                      | Medium                        |

|                             |                       | Linewidth<br>Reduction  | N/A                      | Good                 | Good                 | Good                        | Best                                           | Good                          |

|                             |                       | Assembly Size           | Large                    | Medium               | Medium               | Small                       | Small                                          | Smallest                      |

|                             |                       | On-chip                 | No                       | No                   | No                   | Yes                         | Yes                                            | Yes                           |

|                             |                       | Packaging Style         | KGD                      | KGD                  | KGD                  | KGD                         | All or nothing                                 | All or nothing                |

Adapted from: Shekhar, S., Bogaerts, W., Chrostowski, L., Bowers, J. E., Hochberg, M., Soref, R., & Shastri, B. J. (2023). Silicon Photonics--Roadmapping the Next Generation. *arXiv preprint arXiv:2305.15820*.

#### **AIM Laser Integration for On-chip Light Sources**

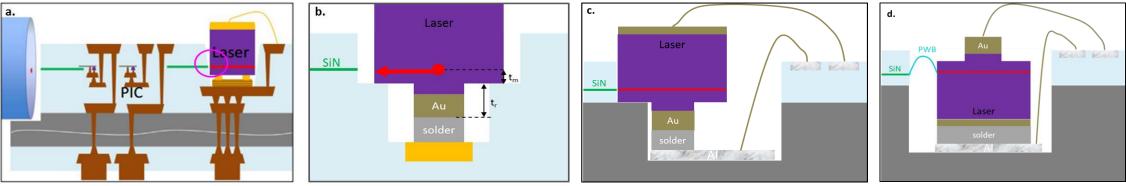

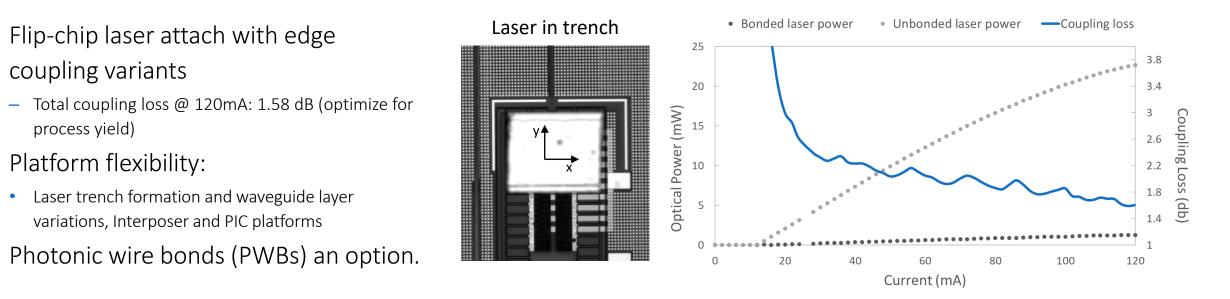

a. Cross-section of the active interposer with a flip-chip attached III-V laser source. b. Detailed structure of laser reference layer to output mode (t<sub>m</sub>), reference layer to Au bond pad (t<sub>c</sub>), and dielectric shelves for laser placement. c. Schematic of laser attach on AIM Photonics PIC MPW platform (only interfacial layers indicated). d. Integration variant of c. using photonic wire bonding (PWB) instead of butt coupling (requires much deeper Si trench since laser is not flipped). NOTE: figures not to scale.

process yield)

\_

٠

AIM Photonics Foundry providing Co-Process and Co-Development to Address Challenges in Photonic Integrated Circuit (PIC) Packaging

### Photonic packaging optical coupling methods

Photonic needs to be more like electronic couplers for sustainable low cost. Difficult to achieve specs in HVM

| Technique             | Loss    | Polarization | Bandwidth          | 1 dB Alignment<br>Tolerance | Density                             | Comment                                         |

|-----------------------|---------|--------------|--------------------|-----------------------------|-------------------------------------|-------------------------------------------------|

| Gratings              | >1.5 dB | TE, TM       | 30-80 nm<br>(1 dB) | 2 µm                        | $\overline{\mathfrak{S}}$           | Highest loss but simplest to test and couple to |

| Edge Coupling         | >0.4 dB | TE & TM      | >100 nm<br>(3 dB)  |                             | ٢                                   | Alignment time                                  |

| Evanescent            | 0.13 dB | TE & TM      | >300 nm<br>(1 dB)  | >2.8                        |                                     | Requires exposed waveguides<br>+ alignment      |

| Microlenses           | >1.7 dB | TE & TM      |                    | 30 µm                       |                                     | Alignment critical, mechanical coupling         |

| Photonic<br>Wirebonds | >0.5 dB | TE & TM      | 300 nm<br>(1 dB)   |                             | $\overline{\mbox{\scriptsize (S)}}$ | Writing time + loss                             |

| Free Space<br>Polymer | 0.5 dB  | TE & TM      | 100 nm<br>(1 dB)   | 6 μm                        | ©                                   | Potential 3D and vertical                       |

Also see L. Ranno, et. al., "Integrated Photonics Packaging: Challenges and Opportunities," ACS Photonics 2022, 9, 3467–3485

#### **Grating Coupling and Co-Process Co-Design**

- Advantages and Uses:

- Easy alignment (±1 mm)

- Wafer level coupling so extensively used in wafer level characterization

- Potential for High Density (with 2D arrays)

- Disadvantages:

- High coupling loss (Typ. 3-4dB)

- Low bandwidth (<100nm)</li>

- Polarization sensitive, angular dependence

- Co-Process and Co-Design

- Requires careful design and optimization using existing process features

"Exploring the Methods, Challenges, and Solutions for

10

**Example Grating**

Structure

## Edge Coupling Co-Process & Co-Design

# ØNYCREATES

- Advantages of coupling over other methods

- Low coupling loss (<3dB) achievable</li>

- Broad bandwidth (>100nm)

- Polarization maintaining

- Disadvantages

- Poor alignment tolerance

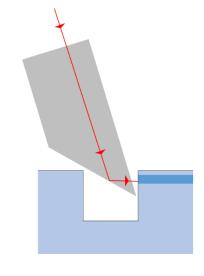

- Efficient coupling to SMF28 requires thick oxide or Silicon substrate removal/undercut

- Lower channel density (along the edge)

- Requires edge preparation (etch or polish)

- Difficult on wafer measurements

- Co-process Co-Design

- Edge coupling structure for improved alignment tolerance

- Thick oxide or Silicon substrate removal/undercut

- Requires edge preparation (etch or polish)

- Passive vs. active alignment

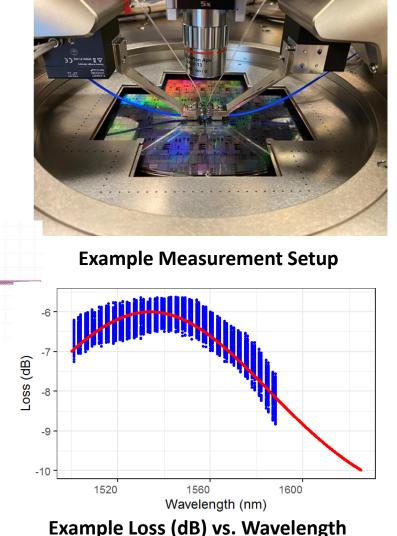

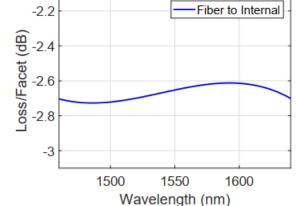

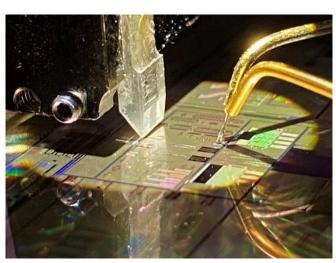

Example Edge Coupler measurement setup

Example Edge Coupler Loss/Facet (dB) vs wavelength measurement

Example Wafer Level Edge Coupler Measurements

#### **Low-Loss Coupling**

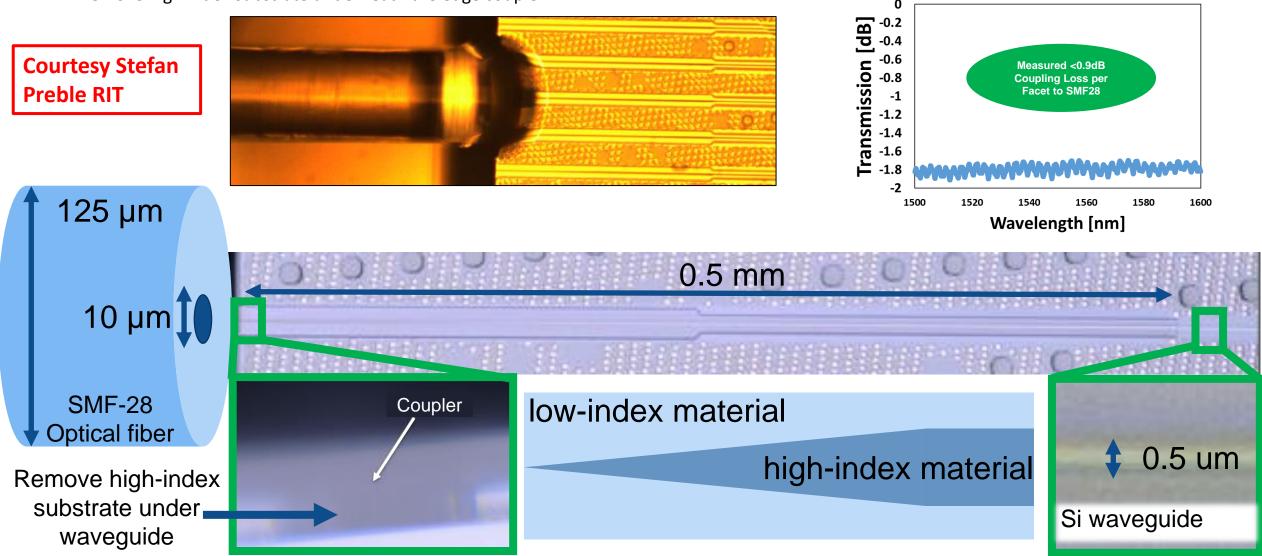

"Exploring the Methods, Challenges, and Solutions for PIC Packaging," Stefan Preble, Photonics Media 2023

PHOTONICS

- Low-loss coupling directly to SMF28 (<1dB/facet)</li>

- Remove high index substrate underneath the edge coupler

#### **AIM Photonics Design-Assembly-Test Enablement Platform**

**ØNY**CREATES

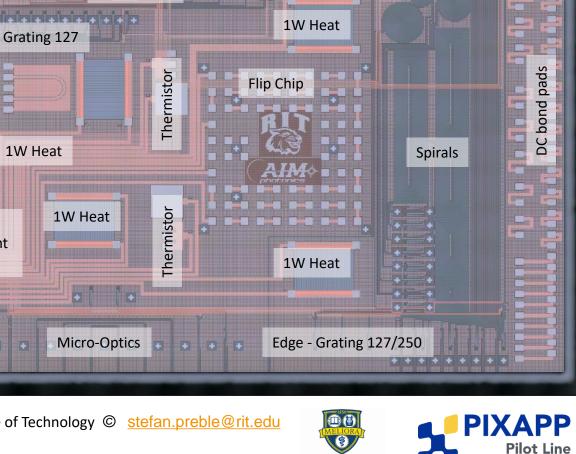

#### **AIM Packaging Reference Chip for Standards**

Reference chips facilitate the development of robust packaging processes and benchmarking of capabilities

- Edge and Grating Couplers

- Standard Pitches and Mode Sizes

- Photodetectors for active alignment

- **RF & DC Electrical Test Structures**

- Flip Chip Electronic IC Integration

- Heaters and Thermistors

- Platform for continuous innovation

Edge 250

Grating 250

Edge 127

+ + +

RF

PD bond Pads

Electrical Component

**Bond Pads**

Edge - Grating 127/250

- Co-process Co-design is critically important for low cost low loss integrated photonic packaging

- AIM Photonics has both the PIC side and the packaging side which enables codesign and an end to end "accessible" flow

- Innovation requires facilities with access to basic electronic and photonic packaging processes to try out new solutions

- It is important to leverage already existing electronic packaging assembly processes and tools in co-packaged optics designs.

- Standardization is key for the industry to develop low cost solutions