## Semiconductorization of Photonics using Silicon Optical Interposer

PIC Conference April 2024

Raju Kankipati

#### Topics

- Optical Interposer platform

- "Semiconductorization of Photonics"

#### Silicon Optical Interposer platform

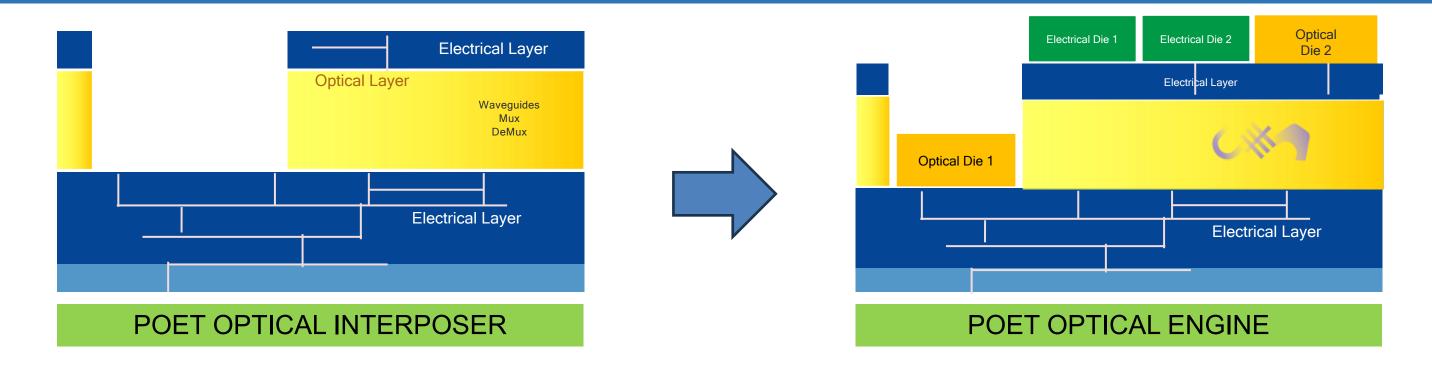

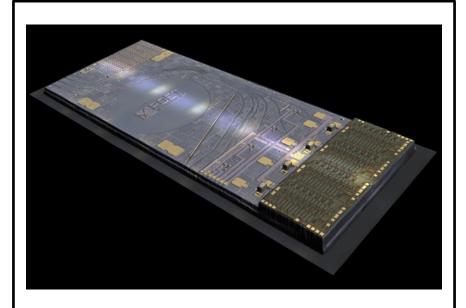

- Integration platform that combines photonics and electronic devices in the same chip-scale package

- Two layers of low loss optical interconnects

- Multiple electrical redistribution layers with low RF insertion loss

- High throughput visually assisted passive "pick and place" assembly of electronics and photonics ICs and components

- In plane and Out of plane Optical Interfaces

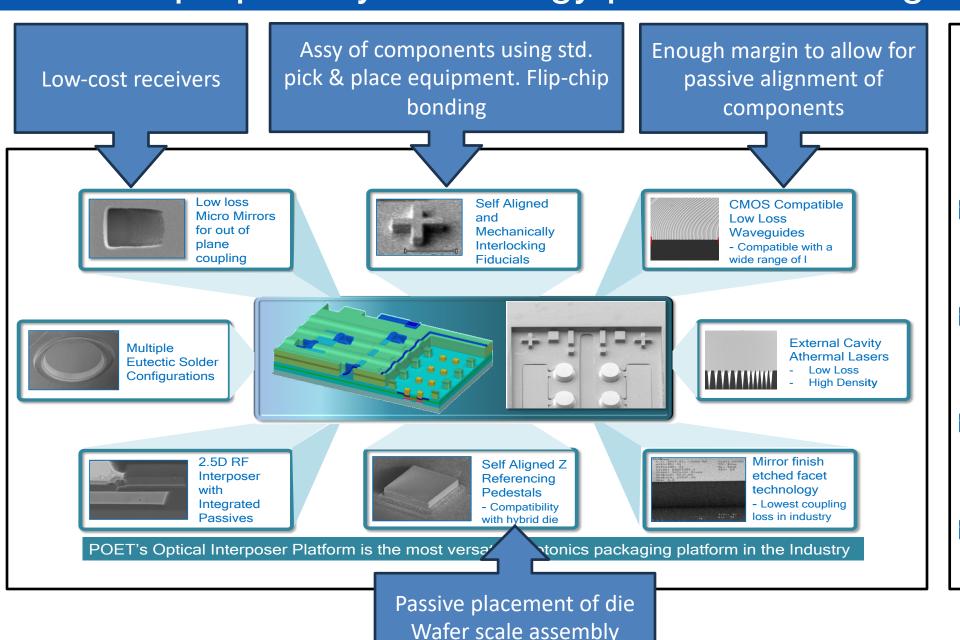

#### Key features of the Interposer platform

#### A proprietary technology platform for integrating photonic solutions

- Drives down the cost of component integration and packaging

- Improves performance and lowers energy consumption

- Miniaturizes and simplifies the design and construction of complex systems

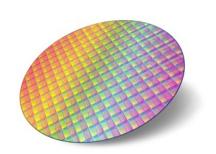

- Provides unparalleled scale through wafer level processing

#### Topics

- Optical Interposer platform

- "Semiconductorization of Photonics"

#### "Semiconductorizing" Photonics

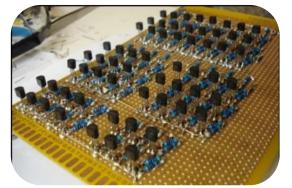

#### POET does for Photonics what Integrated circuits did for electronics

Semiconductor Electronics

#### Discrete Components

#### **Integrated Circuit**

#### Moore's Law

- Smaller, Faster, Cheaper, Volume

- Transformed the industry pervasive presence of semiconductors

- Trillion dollar industry grown over three decades of investment

**Photonics**

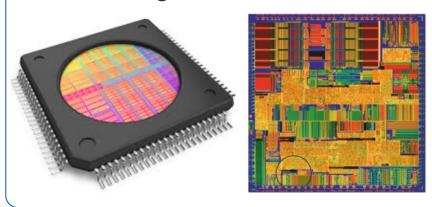

#### Discrete Transceiver Assembly

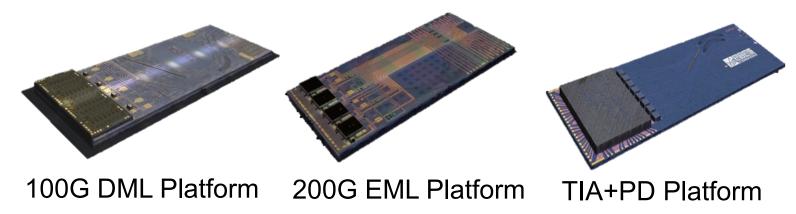

100G

400G

~50 individual components and sub-systems

High labor and equipment cost - cannot scale

# Monitor Photo Diodes High Speed PDs Thermistor Pad World's smallest optical engines for pluggable applications

#### **POET Optical Interposer Platform**

- Automated integration of components on a single chip

- Economies of scale comparable to semiconductors

- Transformational technology for Photonics

#### "Semiconductorizing" Photonics

#### Wafer scale assembly. Passive alignments. Eliminate wire bonds.

### Wafer Level Packaging & Testing

- Use automated pick-place equipment to enable high speed and low-cost manufacturing

- Reduce industry assembly costs from as much as 70% to less than 20%

- Passive Laser placement with high coupling efficiency

- Significant departure from component level testing which much of the industry does

#### **Passive Alignments**

- Eliminate active alignments of Lasers to lens, isolators and optical MUX

- Significant reduction of CapEx and OpEx by eliminating active alignments

- Enables high volume production without large investments

#### **Eliminate Wire bonds**

- Achieve semiconductor type placement of Optical Engines on PCB with solder bumps (no more wire-bonds

- Improve RF performance with high-speed trace instead of gold wire bonds

- Reduce cost

#### Advantages of Optical Interposer

1 Scalable platform

10G/Lane to 200G/Lane with similar architecture, similar assembly process and similar chip size

2 Hybrid Integration

Use best of breed components & material systems: InP (EML, DML, PDs), Silicon Photonic modulators, TFLN

100G CWDM4: 25G/Lane 800G FR4: 200G/Lane

Passive Alignments

Wafer scale assembly & testing for high volume production with lower CapEx

#### Example of platform versatility

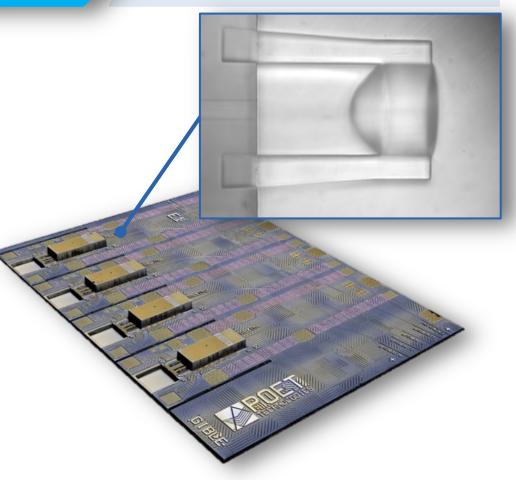

**Step 1-3D printed elements**

**Step 2- passive alignment**

Step 3- PWBs with relaxed alignment tolerances

Collaboration to incorporate 3D-lithography technology into POET's Optical Interposer<sup>TM</sup>

POET's Optical Interposer™, integrates electronic and photonic devices into a single multi-chip module

Micro-optics printed to products with passively aligned lasers

- Maximize coupling efficiency

- Improved coupling efficiency shall reduce power consumption

Initially micro-lenses shall be 3D-printed to the POET's LightBar<sup>™</sup> product to validate the power efficiency improvements and the viability of chip scale wafer level manufacturing

#### Topics

- Optical Interposer platform

- "Semiconductorization of Photonics"

#### Commercializing Optical Interposer!

#### Optical Interposer based solutions

#### **800G FR4 Transmitter**

- Integrated EMLs and EML Driver

- Integrated MUX

- Monitor PDs & Thermistors

- Chiplet architecture to support 800G/1.6T

#### **2X400G FR4 Transmitter**

- Integrated EMLs and EML Driver

- Integrated MUX

- Monitor PDs & Thermistors

- Chiplet architecture to support 400G/800G

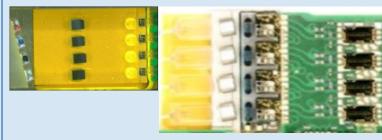

#### 800G 2xFR4 Receiver

- 8xHighspeed PDs

- Integrated TIA

- Integrated DMUX

- TSVs coming soon!

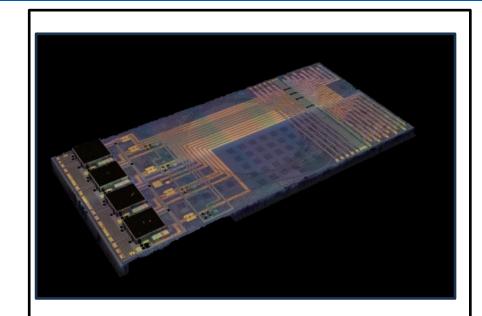

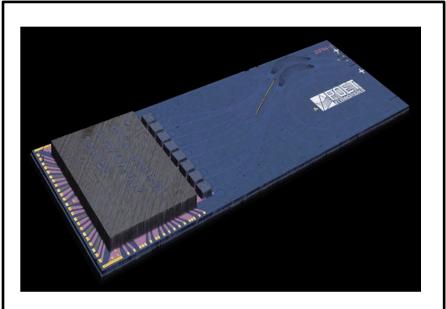

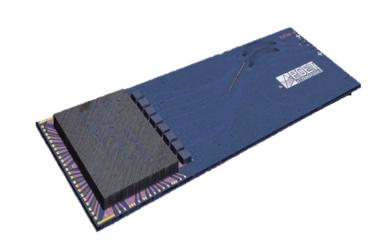

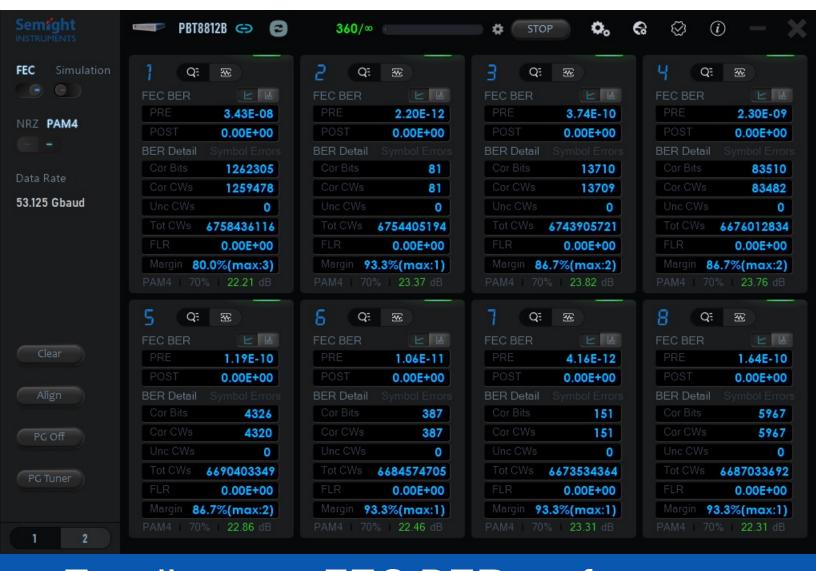

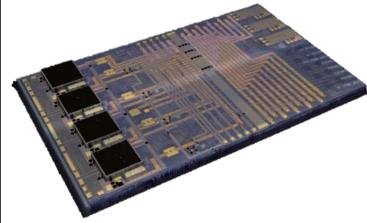

#### 800G 2xFR4 Receiver Optical Engine

- ☐ Integrated 8 channel TIA, high-speed

Photodiodes, Optical DMUX and Fiber Array Unit

- ☐ TIA and PDs flip-chip attached: No wire-bonds between TIA and PD

- □ DMUX monolithically integrated on the interposer

- ☐ Small chip size: 5.1 x 14.8 mm (W x L)

Excellent pre-FEC BER performance

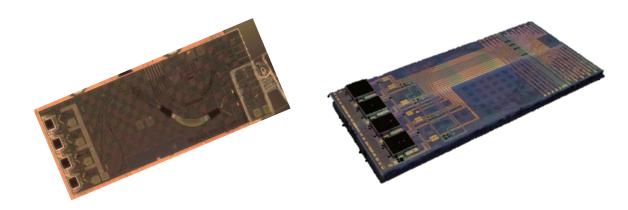

#### 1.6T Pluggable transceiver using POET Engines

#### 1.6T DR8 & 2xFR4 Solution

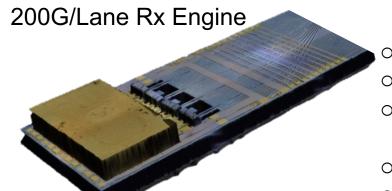

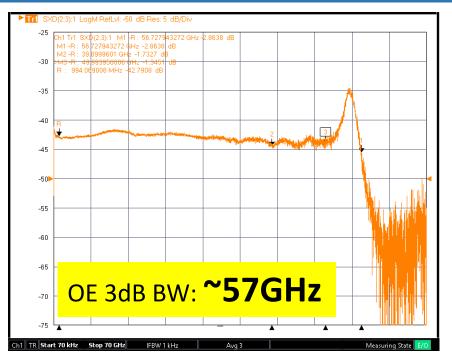

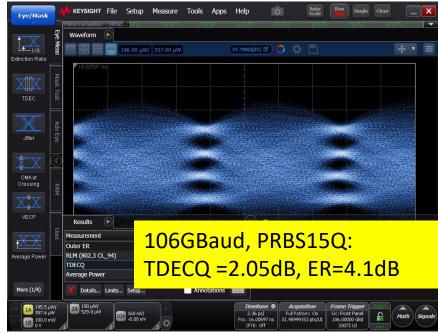

200G/Lane Tx Engine

- EML Lasers (1310nm)

- Integrated EML Drivers

- SMF mode matched SSC for easier fiber alignment

- Integrated MPDs & thermistor

- Integrated MUX (for FR4)

- Chip size: 4.75 x 7.7 mm

- PIN-PDs

- Integrated Quad TIA

- SMF mode matched SSC for easier fiber alignment

- Integrated DMUX (for FR4)

- o Chip size: 3.75 x 7.7 mm

#### Summary

Higher speed communication requires high level of integration between electronics and photonics

The Optical Interposer provides high speed RF trace on the platform and eliminates the use of wire-bonds

Limiting to one material system (like silicon photonics) may not offer the best cost and performance solution

Using best of breed and known-good components accelerates time to market and provides best cost and performance

Scaling to high volume with lower CapEx requires "Semiconductorization of Photonics"

The Optical Interposer uses passive attachment process for photonics and enables wafer scale assembly