# Revolutionizing Architecture and Components for New Generation Energy-Efficient High-Density Photonic Integrated Coherent Transceivers

Tomoyuki Akiyama<sup>1,2</sup>, Yohei Sobu<sup>1,2</sup>, Shinsuke Tanaka<sup>1,2</sup>, Hisao Nakashima<sup>2</sup>, and Takeshi Hoshida<sup>2</sup> <sup>1</sup>PETRA <sup>2</sup>Fujitsu Ltd.

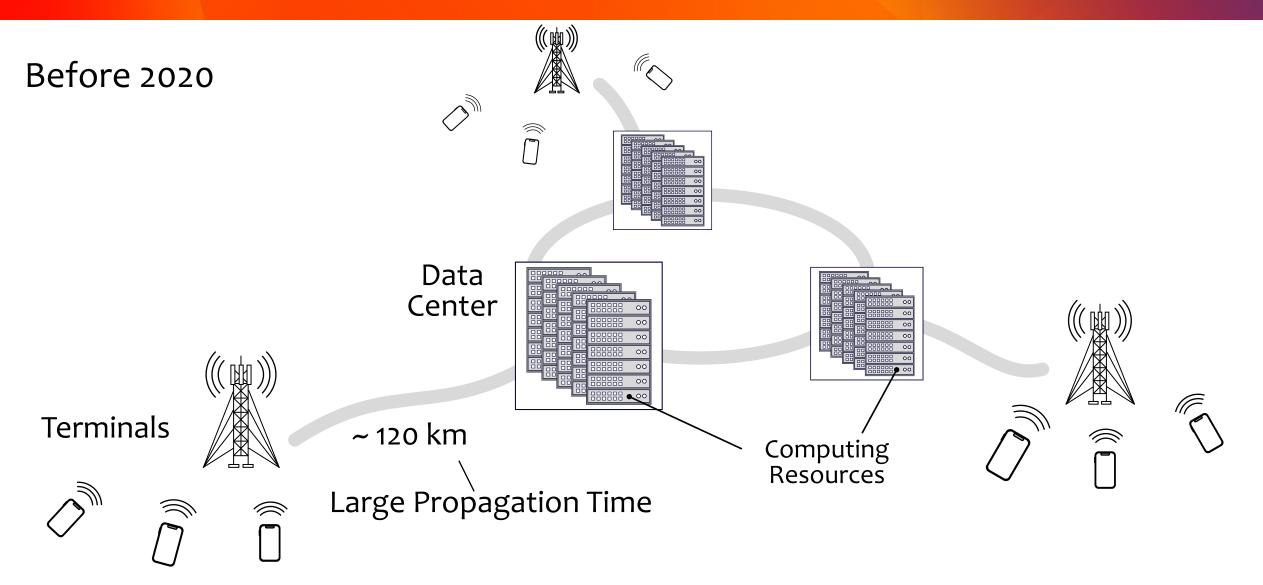

# Network Evolutions Toward 2030's

**PETRA** FUJITSU

Limits Applications to OnlyThose Tolerating Large Latency

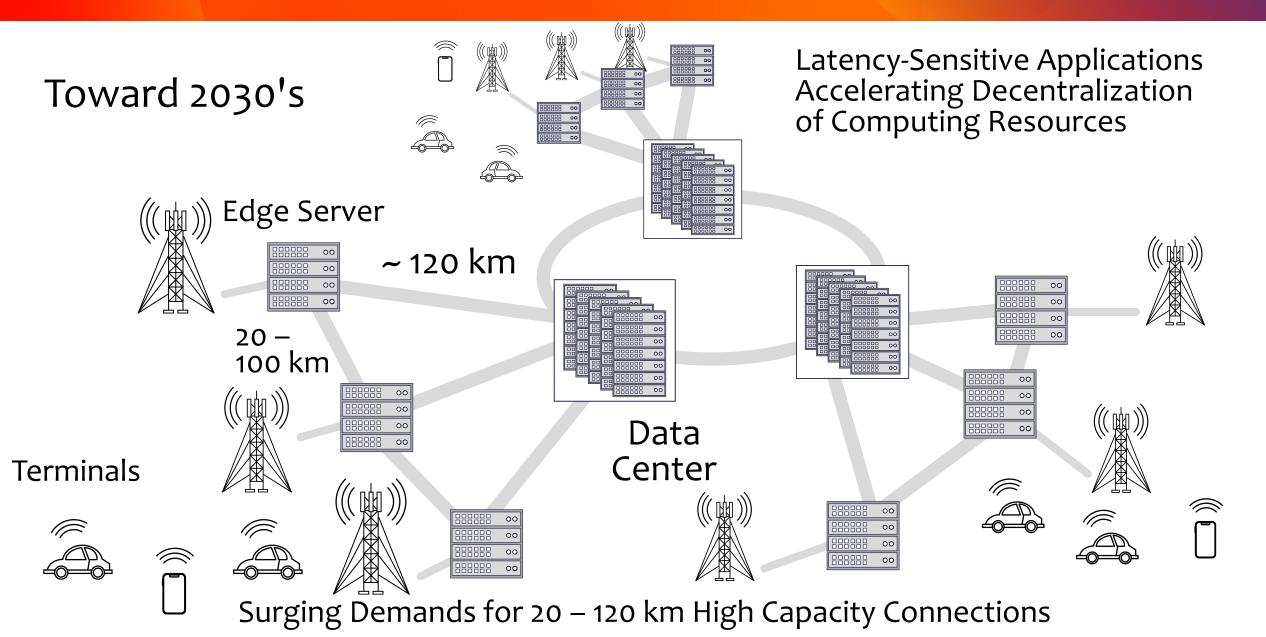

# Network Evolutions Toward 2030's

**PETRA** FUJITSU

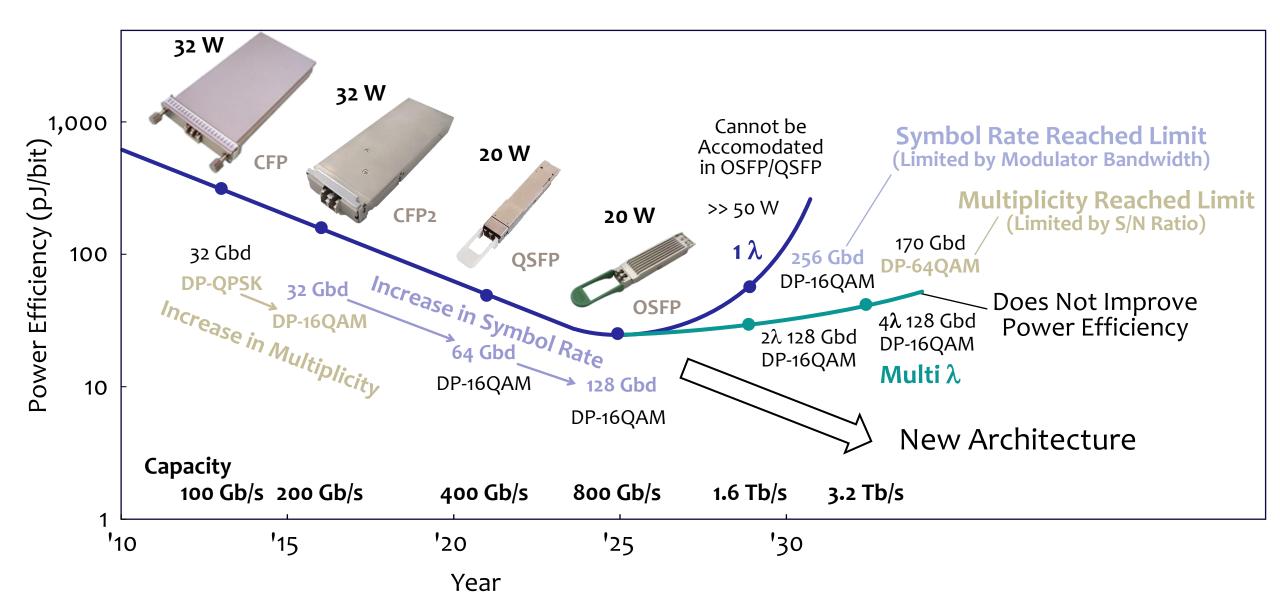

### Trend of Pluggable Transceiver Power Efficiency PETRA FUJITSU

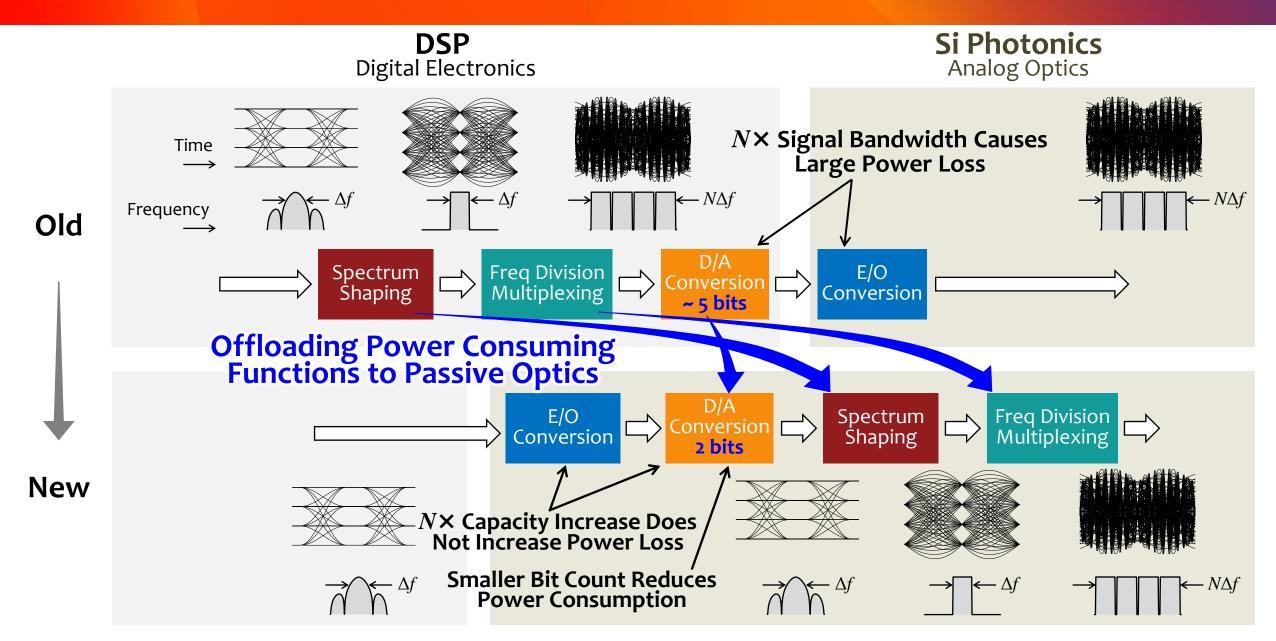

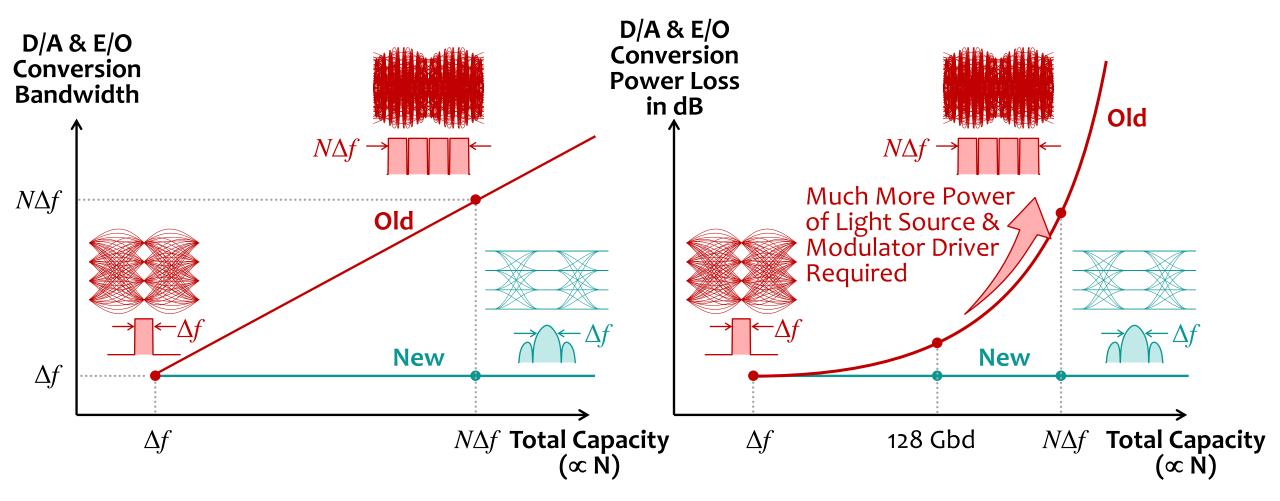

# New Generation Transceiver Architecture

#### **Benefits : Drastic Reduction of Power Consumption**

D/A & E/O Conversion Loss  $\downarrow \Rightarrow$  Light Source & Modulator Driver Power  $\downarrow$

#### **Benefits : Drastic Reduction of Power Consumption**

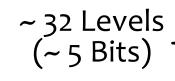

- D/A & E/O Conversion Loss  $\downarrow \Rightarrow$  Light Source & Driver Power  $\downarrow$

- DAC Bit Count,  $N \downarrow 5 \rightarrow 2 \Rightarrow$  DAC Power Consumption  $\downarrow 1/8x (\propto 2^N)$

Old

New

#### **Benefits : Drastic Reduction of Power Consumption**

D/A & E/O Conversion Loss  $\downarrow \Rightarrow$  Light Source & Driver Power  $\downarrow$

- DAC Bit Count,  $N \downarrow 5 \rightarrow 2 \Rightarrow$  DAC Power Consumption  $\downarrow 1/8x (\propto 2^N)$

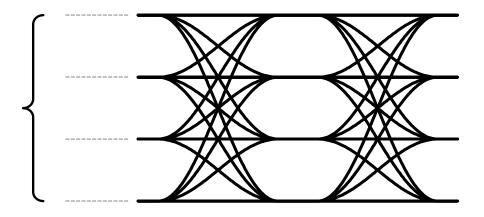

- DAC PAPR  $\downarrow$  10  $\rightarrow$  4 dB  $\Rightarrow$  DAC S/N $\uparrow$  +6 dB  $\Rightarrow$  ADC Noise Margin $\uparrow$   $\Rightarrow$  ADC ENOB  $\downarrow$   $\Rightarrow$  ADC Power Consumption  $\downarrow$

#### **Benefits : Drastic Reduction of Power Consumption**

- D/A & E/O Conversion Loss  $\downarrow \Rightarrow$  Light Source & Driver Power  $\downarrow$

- DAC Bit Count,  $N \downarrow 5 \rightarrow 2 \Rightarrow$  DAC Power Consumption  $\downarrow 1/8x (\propto 2^N)$

- DAC PAPR  $\downarrow$  10  $\rightarrow$  4 dB  $\Rightarrow$  DAC S/N<sup>+6</sup> dB  $\Rightarrow$  ADC Noise Margin<sup>+</sup>  $\Rightarrow$  ADC ENOB  $\downarrow \Rightarrow$  ADC Power Consumption  $\downarrow$

- Power Consumption for Electrical Spectrum Shaping Eliminated

#### **Benefits : Drastic Reduction of Power Consumption**

- D/A & E/O Conversion Loss  $\downarrow \Rightarrow$  Light Source & Driver Power  $\downarrow$

- DAC Bit Count,  $N \downarrow 5 \rightarrow 2 \Rightarrow$  DAC Power Consumption  $\downarrow 1/8x (\propto 2^N)$

- DAC PAPR  $\downarrow$  10  $\rightarrow$  4 dB  $\Rightarrow$  DAC S/N<sup>+6</sup> dB  $\Rightarrow$  ADC Noise Margin<sup>+</sup>  $\Rightarrow$  ADC ENOB  $\downarrow$   $\Rightarrow$  ADC Power Consumption  $\downarrow$

- Power Consumption for Electrical Spectrum Shaping Eliminated

#### **Concerns to be Addressed :**

Loss↑ by Optical Spectrum Shaping → Compensated by DAC Loss↓ (PAPR↓) (+ Only Slight ↑ of Light Source & Driver Power) Loss↑ by Optical (De)Multiplexing → Loss↓ by CAT Technology Novel Technologies Developed for New Generation Transceiver Architecture

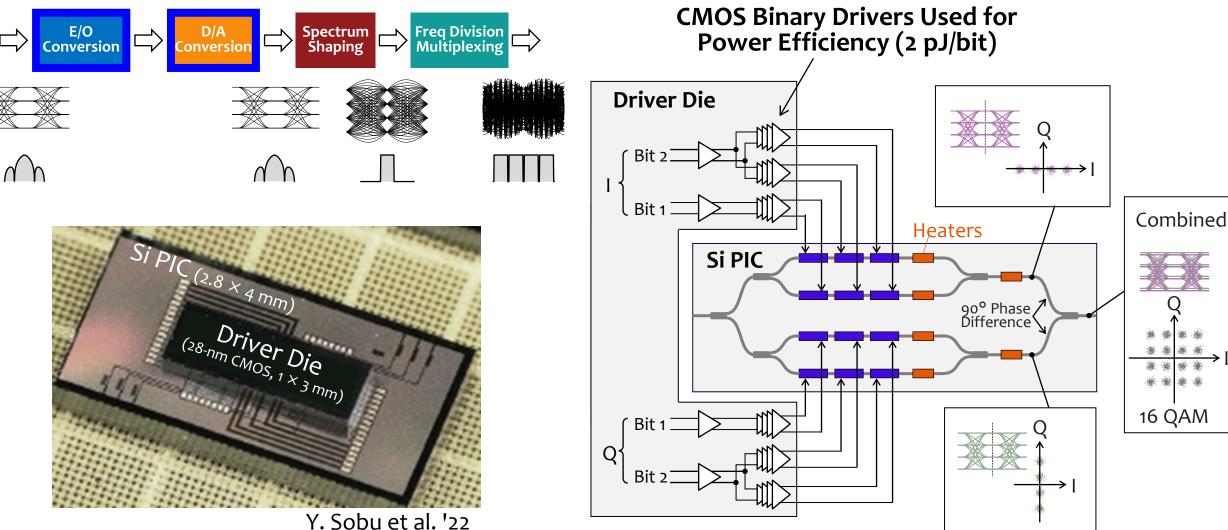

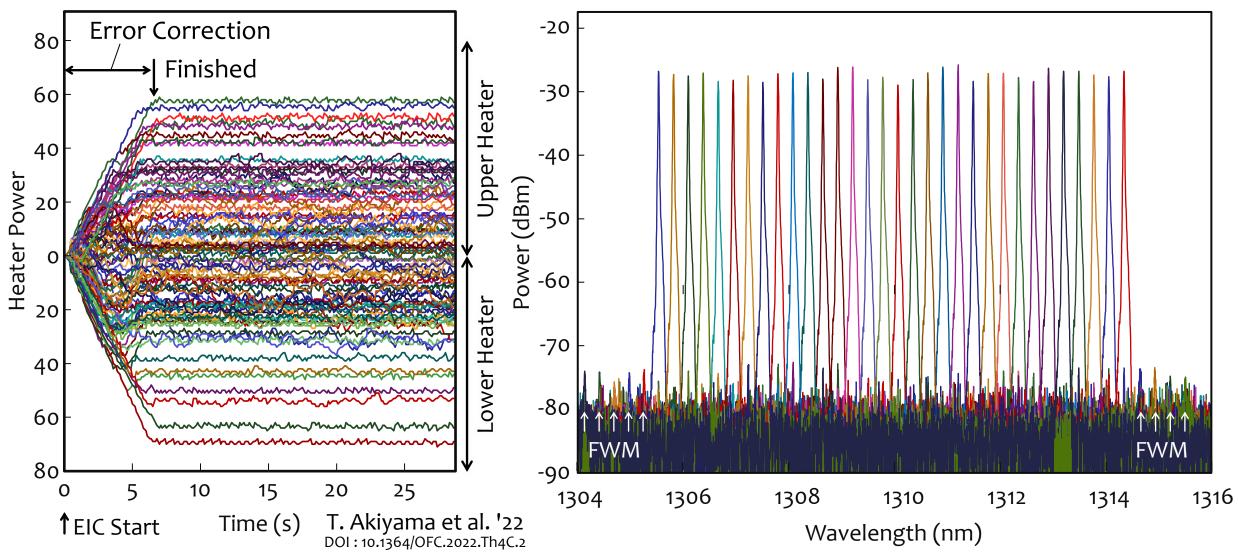

# E/O & D/A Conversion (Optical DAC)

Transmitter

**Petra** fujitsu

Y. SODU et al. 22 DOI: 10.1364/OFC.2022.M1D.4

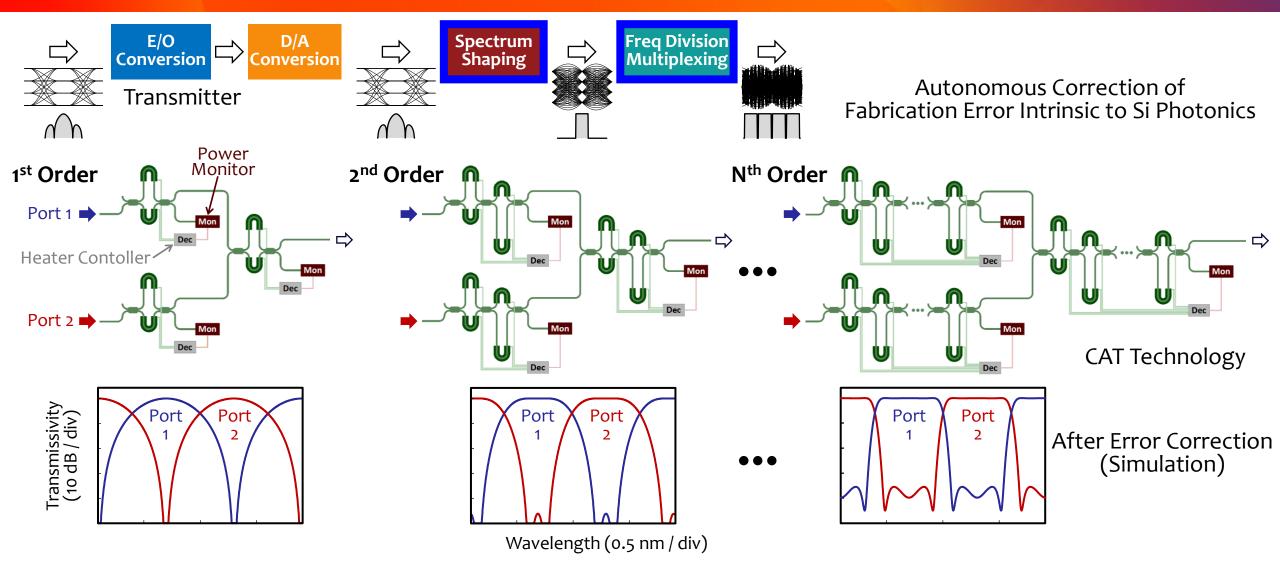

# Spectrum Shaping & Multiplexing

**Petra** fujitsu

Nyquist(-like) Shaping with Reduced DAC Bit Count  $(5 \rightarrow 2)$  for Drastic DAC Power Reduction  $(1/8 \times 2)$  Drastically Reduced Multiplexing Loss  $(6 \rightarrow 2 \text{ dB for 4 Ports}, 9 \rightarrow 3 \text{ dB for 8 Ports}, Compared to Couplers)$

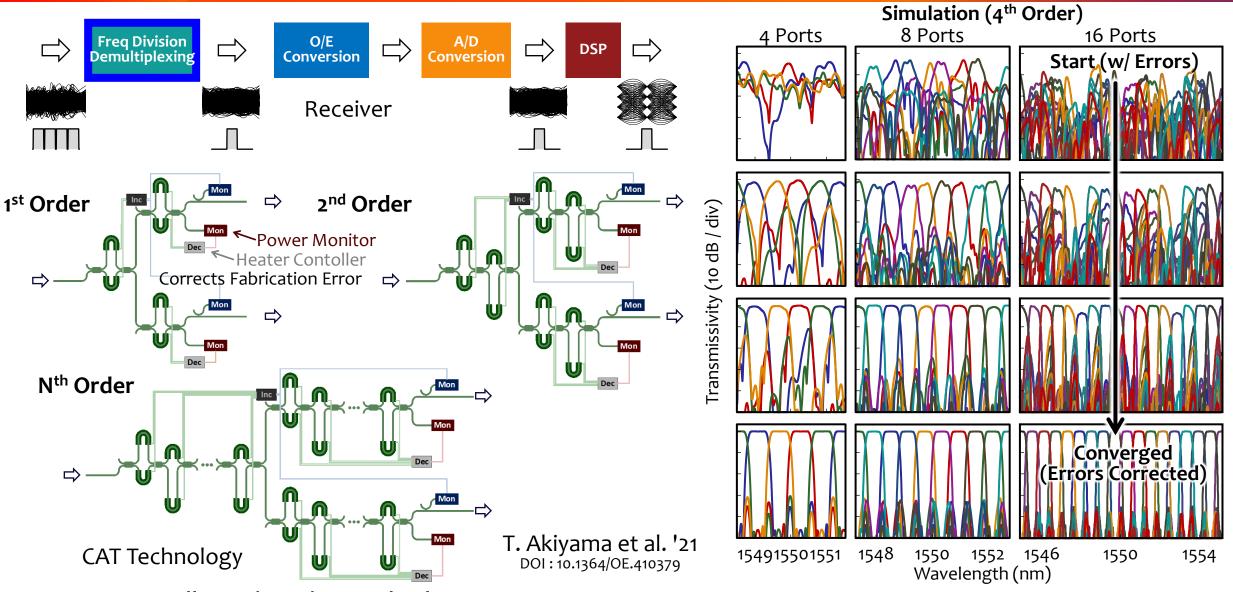

# Demultiplexing

# **Petra** fujitsu

Drastically Reduced Demultiplexing Loss ( $6 \rightarrow 2 \text{ dB}$  for 4 Ports,  $9 \rightarrow 3 \text{ dB}$  for 8 Ports, Compared to Couplers)

### Demultiplexing

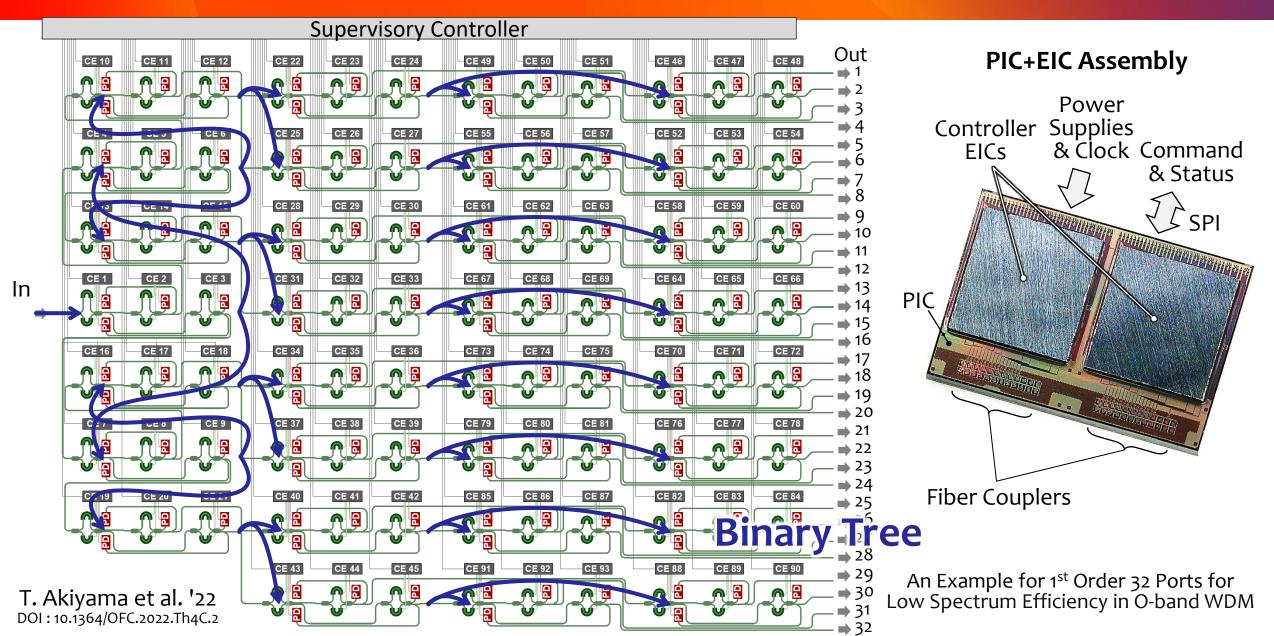

# Demultiplexing

An Example for 1<sup>st</sup> Order 32 Ports for Low Spectrum Efficiency in O-band WDM

### Summary

New Generation Transceiver Architecture Based on Optical DAC and CAT Technology for Capacity Scaling Toward Discentralized Computing Era

Use of Parallelism to Reduce Light Source & Driver Power Consumptions

D/A & E/O Conversion Losses Reduced Combining & Splitting Losses Reduced by CAT Technology

#### 2 Offloading DSP Spectrum Shaping into Optics by CAT Technology to Reduce DAC & ADC Power Consumptions

DAC Bit Count  $\downarrow 5 \rightarrow 2 \Rightarrow$  DAC Power Consumption  $\downarrow 1/8x$ DAC Noise  $\downarrow -6 dB \Rightarrow$  ADC Power Consumption  $\downarrow (ENOB \downarrow)$ Loss Compensated by PAPR  $\downarrow 10 \rightarrow 4 dB \& Only Slight \uparrow of Light Source \& Driver Power$

Power Efficient Optical D/A Converter

#### This presentation is based on results obtained from a project,

JPNP16007, commissioned by the New Energy and Industrial

Technology Development Organization (NEDO).