## Speeding VCSEL Feedback

#### S. Shutts<sup>1</sup>, J. Baker<sup>1</sup>, C. P. Allford<sup>1</sup>, S. Gillgrass<sup>1</sup>, J. I. Davies<sup>2</sup>, P. M. Smowton<sup>1,3</sup>

<sup>1</sup> Future Compound Semiconductor Manufacturing Hub, School of Physics and Astronomy, Cardiff University, Cardiff, UK, CF24 3AA

<sup>2</sup> IQE plc, Pascal Close, St Mellons, Cardiff, UK, CF3 0LW

<sup>3</sup> Institute for Compound Semiconductors, School of Physics and Astronomy, Cardiff University, Cardiff, UK, CF24 3AA

bakerj19@cardiff.ac.uk

Engineering and Physical Sciences Research Council

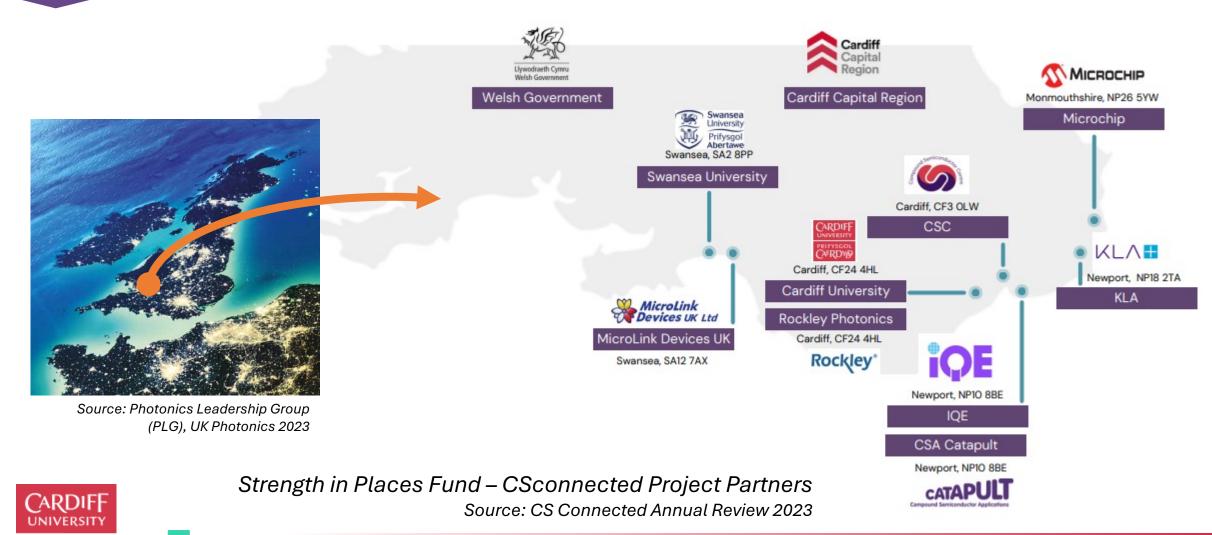

#### South Wales CS Cluster

Engineering and Physical Sciences Research Council

bakeri19@cardiff.ac.uk

### Institute for Compound Semiconductors

- Housed at Cardiff University's

Translational Research Hub

- 12 process engineers/technicians

- Open access facility

CS Hub

- 200 mm (8-inch) capability

- 1350 m<sup>2</sup> clean room

- Bridging the gap between R&D and industry

Engineering and Physical Sciences Research Council

s <u>bakerj19@cardiff.ac.uk</u>

Engineering and Physical Sciences D Research Council

bakerj19@cardiff.ac.uk

**EPSRC Future Compound Semiconductor Manufacturing Hub**

4

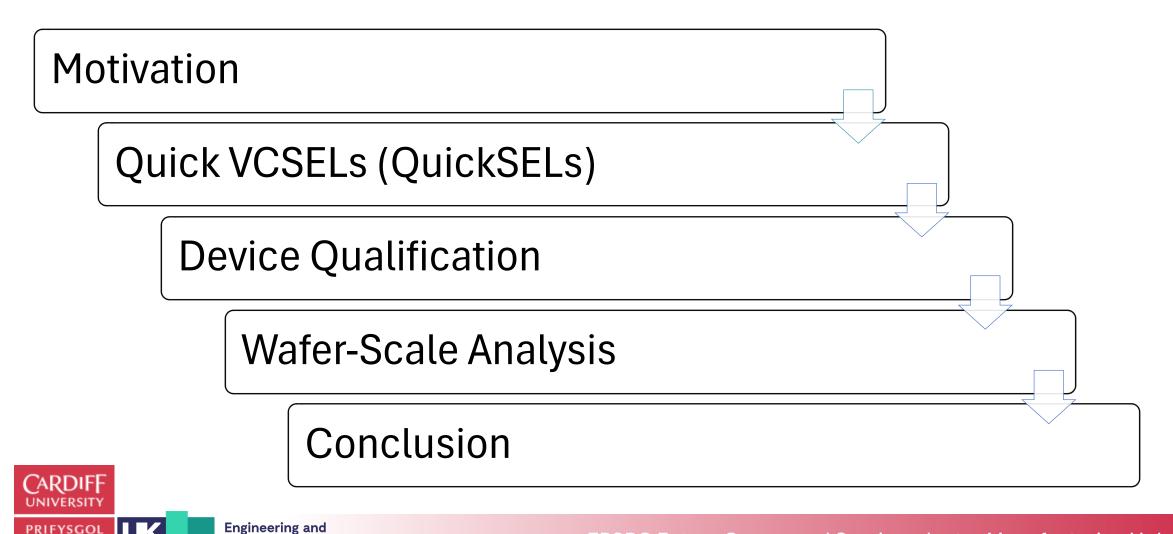

#### **Motivation**

Quick VCSELs (QuickSELs)

**Device Qualification**

Wafer-Scale Analysis

#### Conclusion

Engineering and Physical Sciences Research Council

bakerj19@cardiff.ac.uk

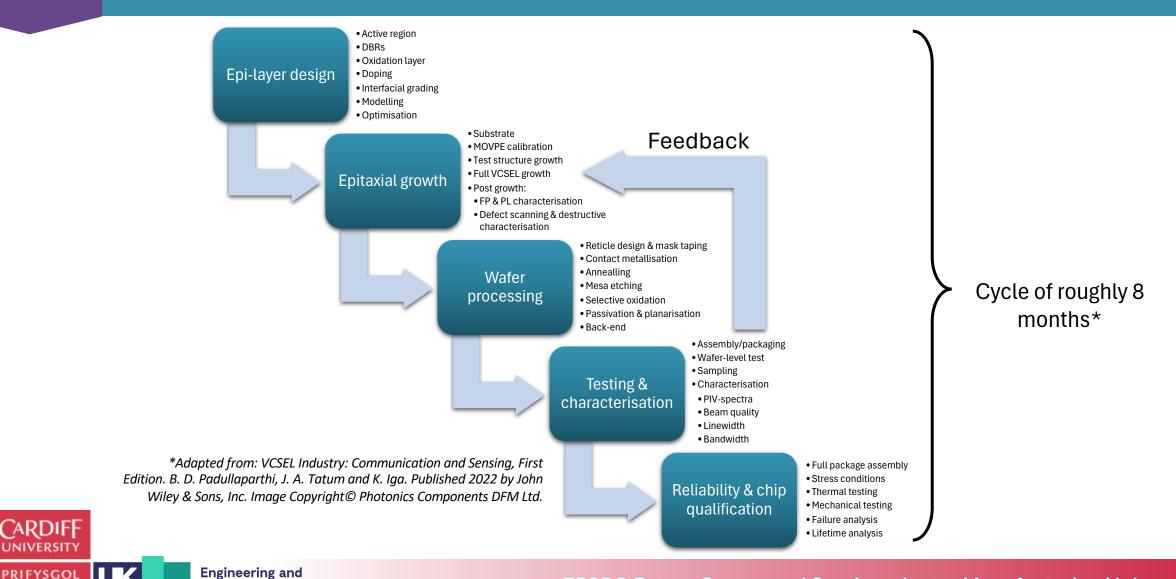

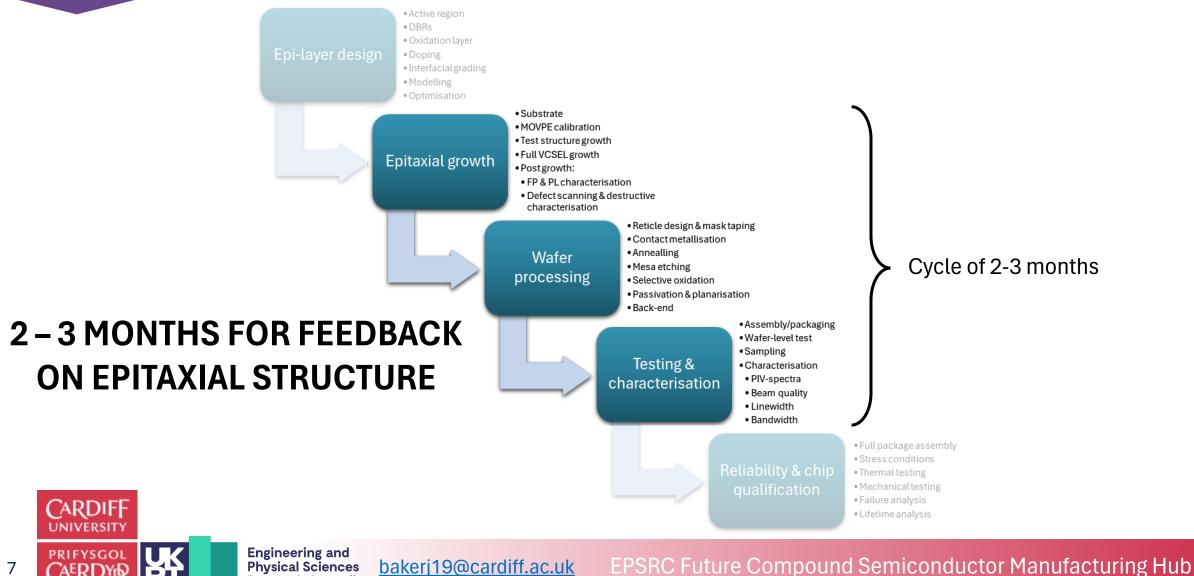

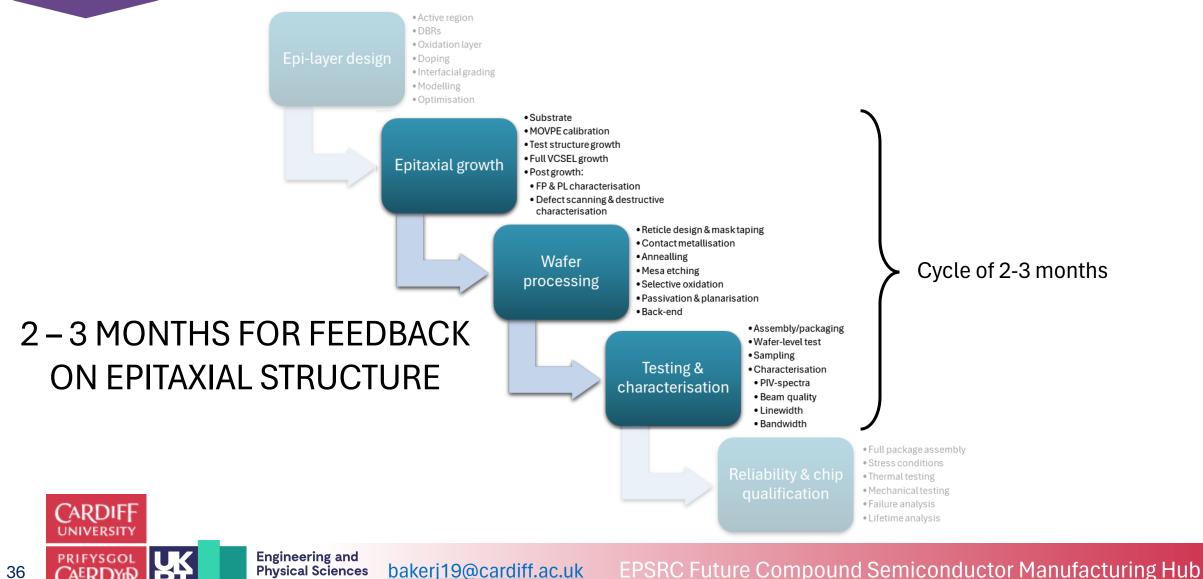

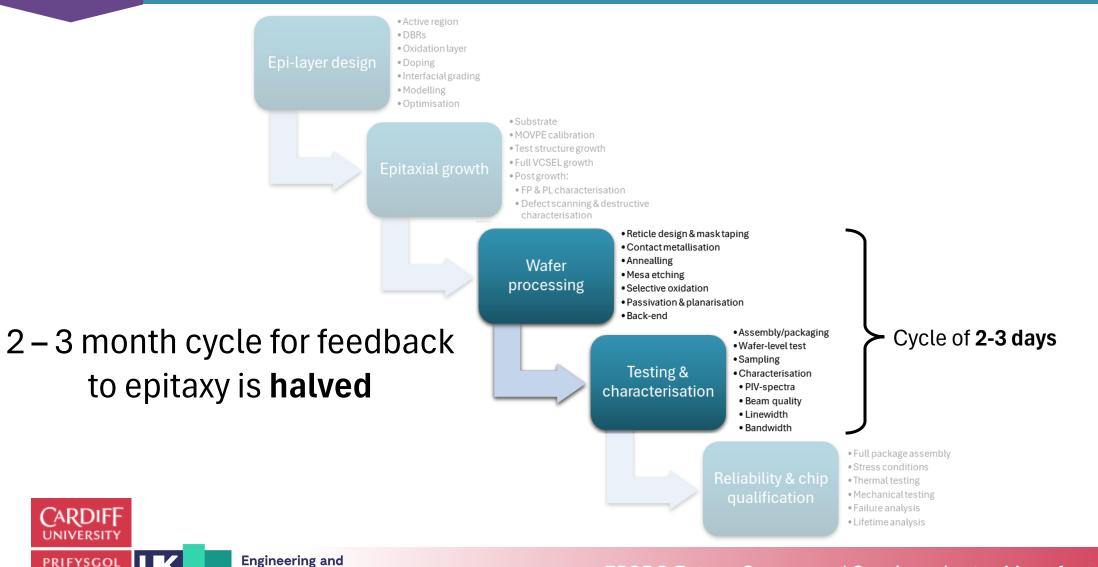

#### VCSEL Product Development Cycle

Engineering and Physical Sciences Research Council

es bakerj19@cardiff.ac.uk

**EPSRC Future Compound Semiconductor Manufacturing Hub**

CS Hub

#### VCSEL Product Development Cycle

**Research Council**

CS Hub

#### Need for a Quick-VCSEL structure which reduces processing time whilst preserving device performance

# Assess quality & uniformity of epitaxial material through wafer-scale testing of QuickSELs

Engineering and Physical Sciences <u>bakerj19@cardiff.ac.uk</u> Research Council

Physical Sciences Research Council

es <u>bakerj19@cardiff.ac.uk</u>

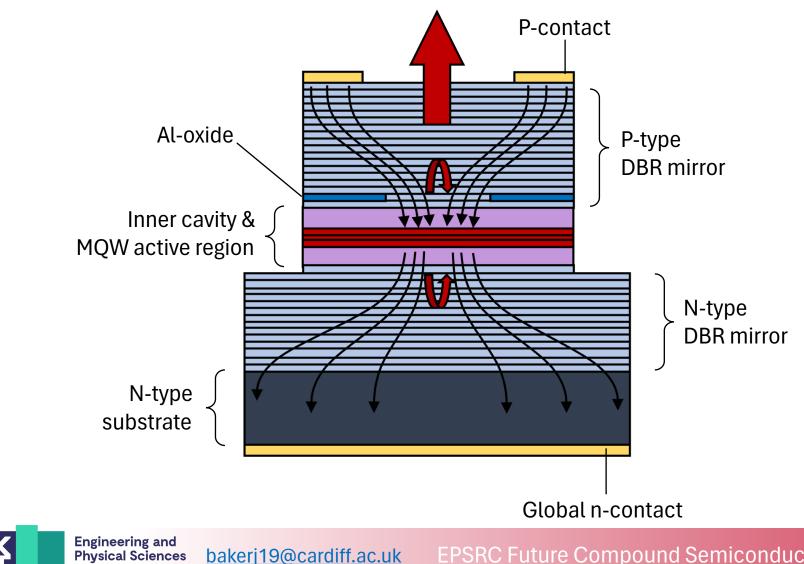

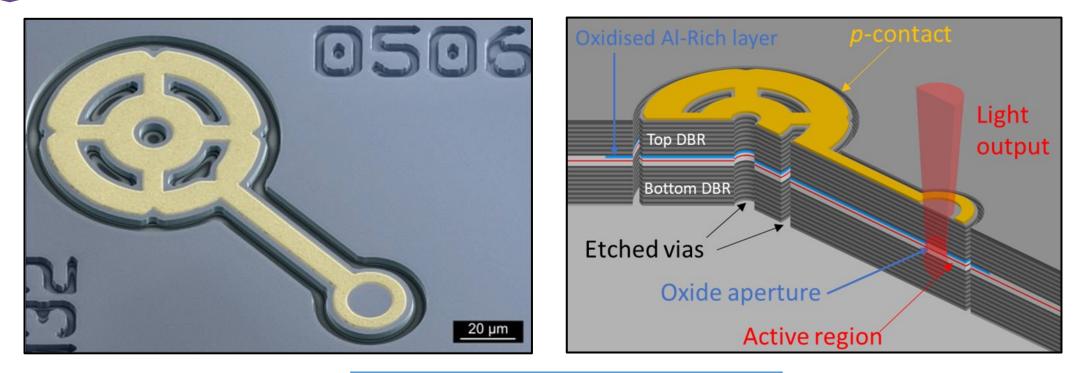

#### CS Hub **Typical VCSEL Structure**

bakerj19@cardiff.ac.uk **Research Council**

**EPSRC** Future Compound Semiconductor Manufacturing Hub

CARDIFF

UNIVERSITY

PRIFYSGOL

ℨℰ℞ⅅℽⅅ

**ARDIF**

11

Total processing time – 24 hours

(vs 24-36 hours per mask layer for a full high performance VCSEL = up to 16.5 days for some structures)

"VCSEL Quick Fabrication for Assessment of Large Diameter Epitaxial Wafers," IEEE Phot. J, 14, 3, 1-10, (2022), doi:10.1109/JPHOT.2022.3169032.

Engineering and Physical Sciences Research Council

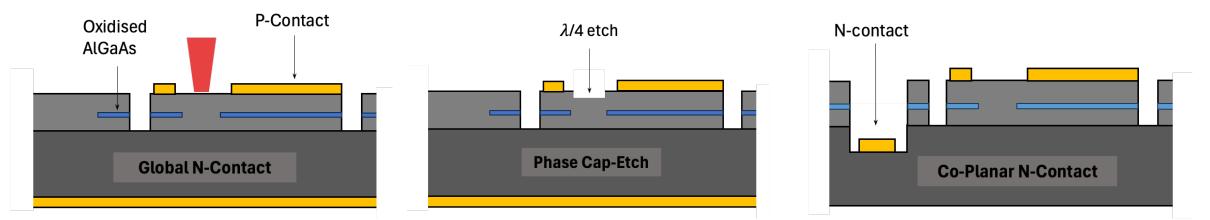

| Market                         | Requirements                    | Growth                           | Device         | Where?    |

|--------------------------------|---------------------------------|----------------------------------|----------------|-----------|

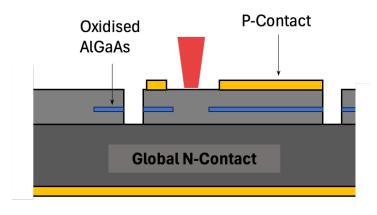

| Sensing/LiDAR                  | High-power                      | Doped<br>substrate               | Global N       | [1]       |

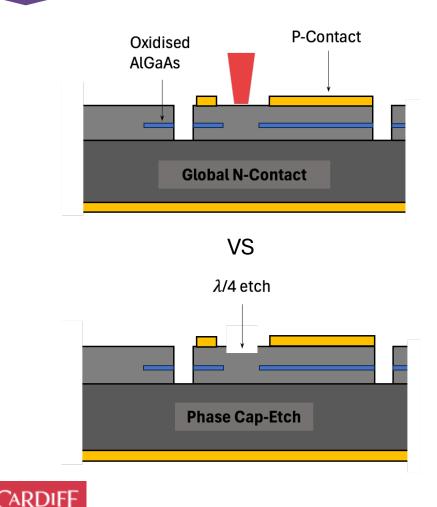

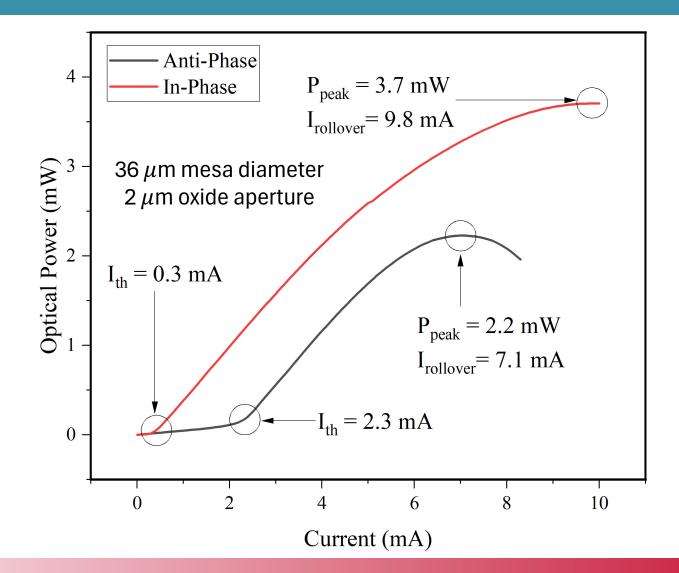

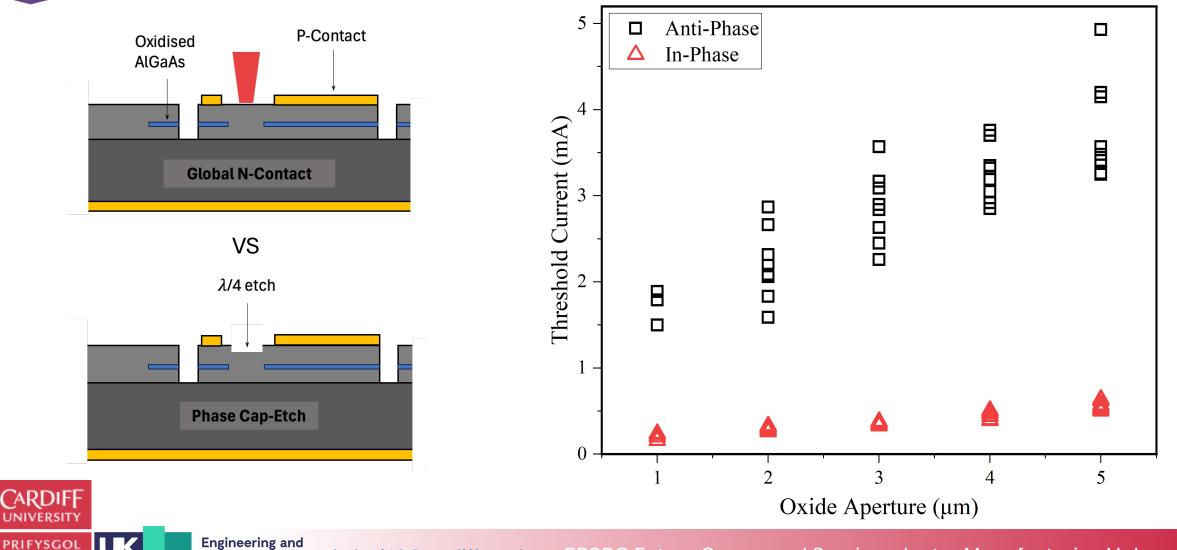

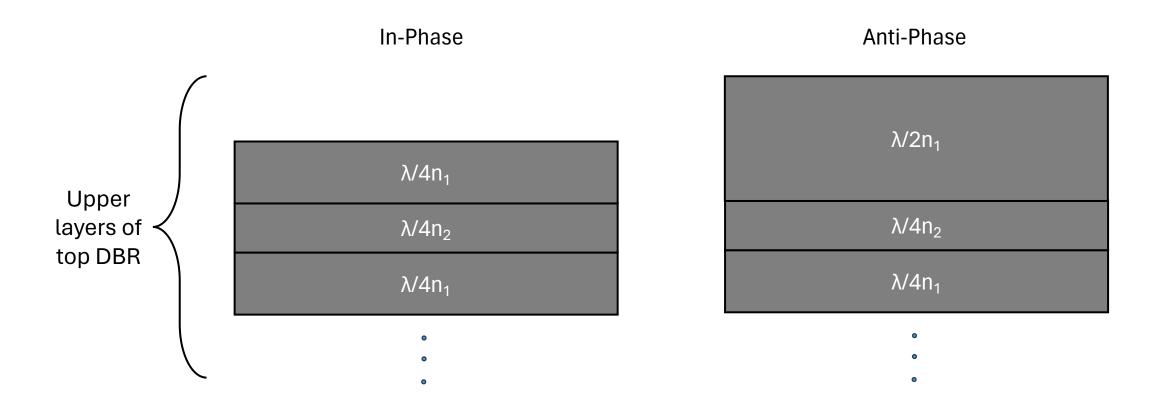

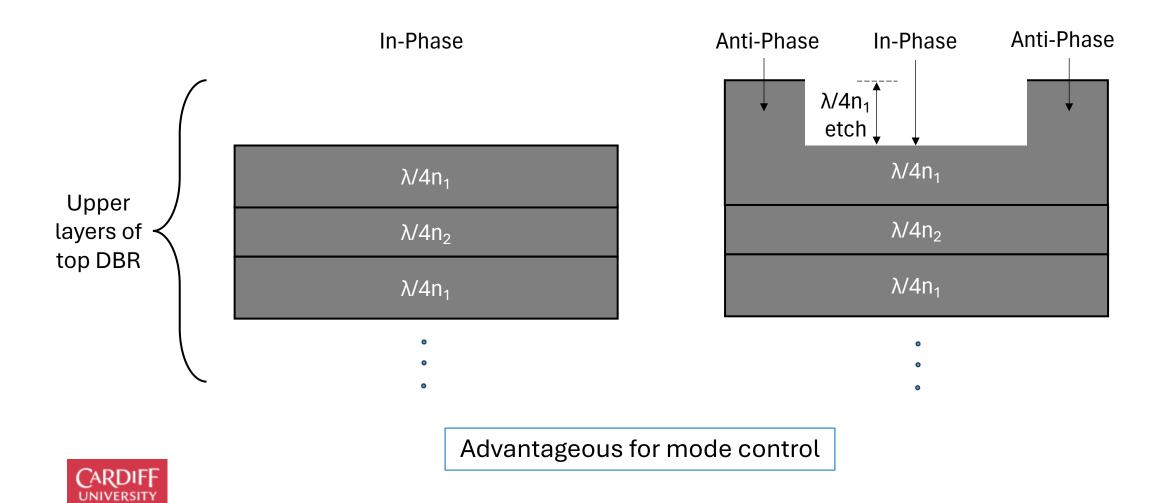

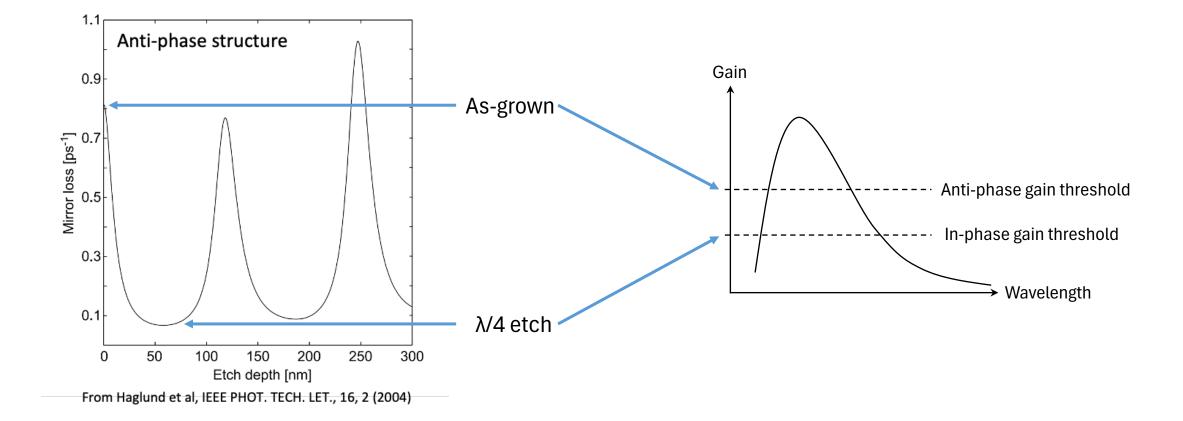

| Atomic<br>clocks/magnetometers | Single-mode<br>Narrow linewidth | Anti-phase<br>cap                | Phase Cap-Etch | This work |

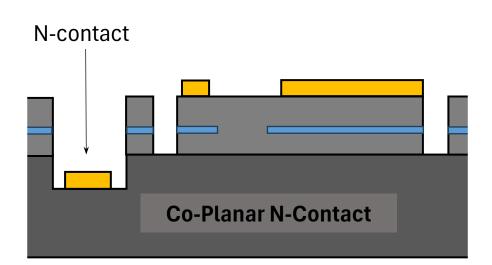

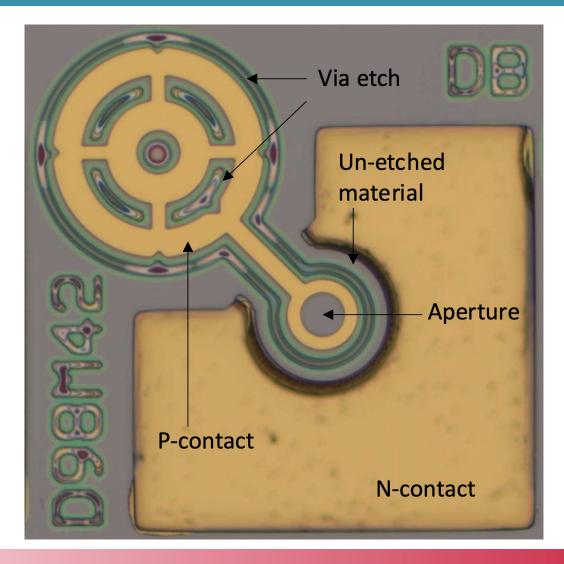

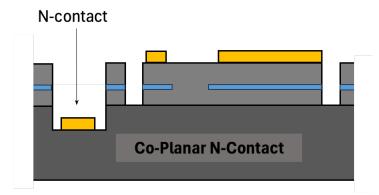

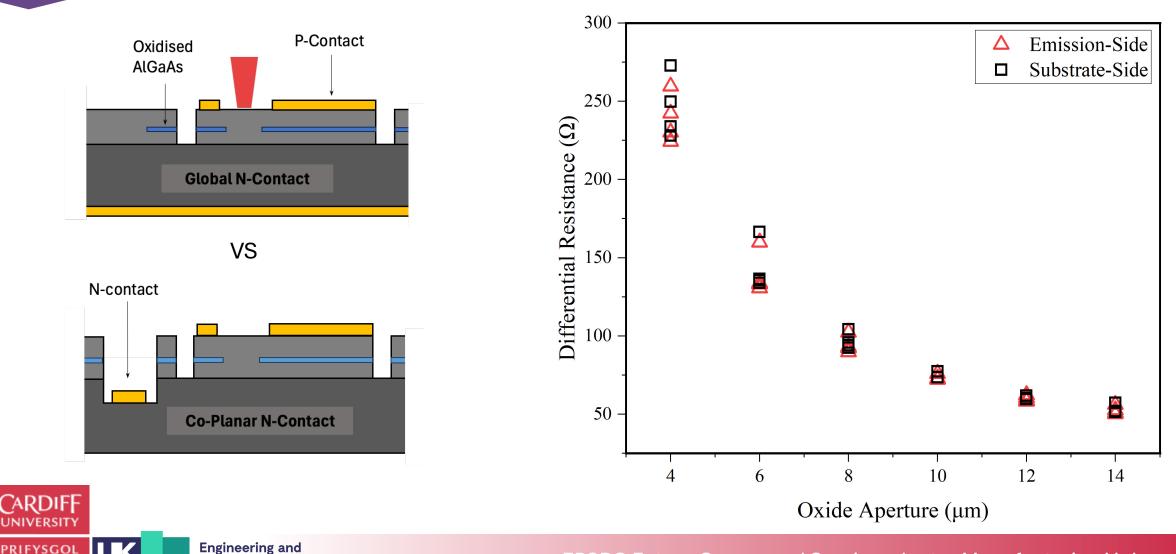

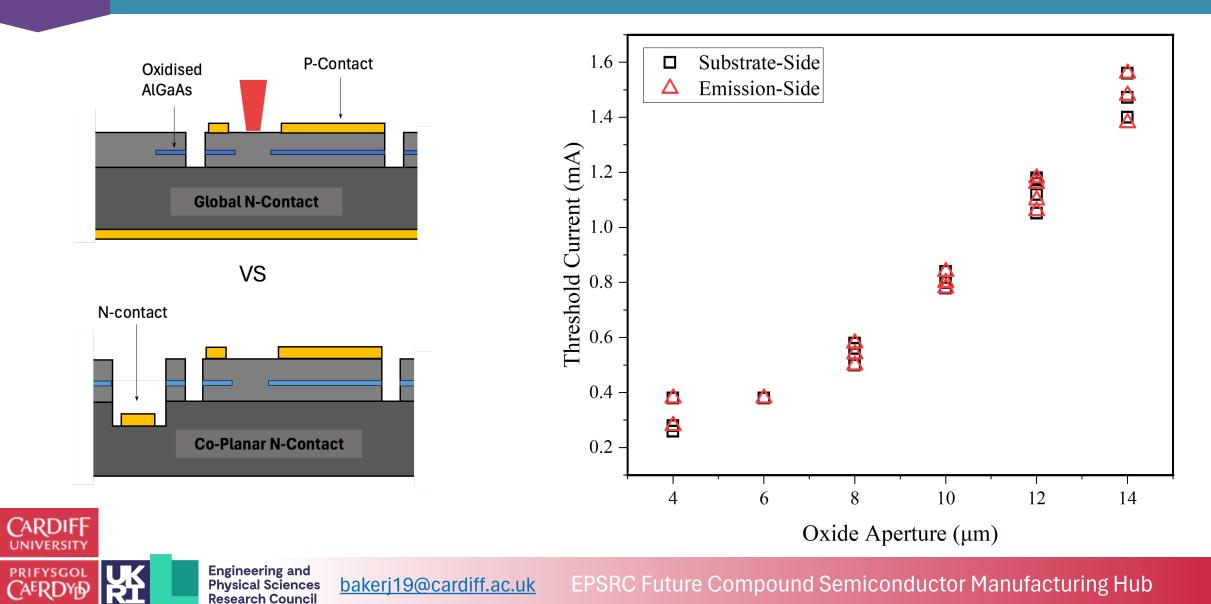

| Datacom                        | High-frequency modulation       | Semi-<br>insulating<br>substrate | Co-Planar N    | This work |

Engineering and Physical Sciences Research Council

bakerj19@cardiff.ac.uk

| Market                         | Requirements                    | Growth                           | Device         | Where?    |

|--------------------------------|---------------------------------|----------------------------------|----------------|-----------|

| Sensing/LiDAR                  | High-power                      | Doped<br>substrate               | Global N       | [1]       |

| Atomic<br>clocks/magnetometers | Single-mode<br>Narrow linewidth | Anti-phase<br>cap                | Phase Cap-Etch | This work |

| Datacom                        | High-frequency modulation       | Semi-<br>insulating<br>substrate | Co-Planar N    | This work |

[1] "VCSEL Quick Fabrication for Assessment of Large Diameter Epitaxial Wafers," IEEE Phot. J, 14, 3, 1-10, (2022), doi:10.1109/JPHOT.2022.3169032.

13

Engineering and Physical Sciences bar Research Council

bakerj19@cardiff.ac.uk

| Market                         | Requirements                    | Growth                           | Device         | Where?    |

|--------------------------------|---------------------------------|----------------------------------|----------------|-----------|

| Sensing/LiDAR                  | High-power                      | Doped<br>substrate               | Global N       | [1]       |

| Atomic<br>clocks/magnetometers | Single-mode<br>Narrow linewidth | Anti-phase<br>cap                | Phase Cap-Etch | This work |

| Datacom                        | High-frequency modulation       | Semi-<br>insulating<br>substrate | Co-Planar N    | This work |

Engineering and Physical Sciences bal Research Council

bakerj19@cardiff.ac.uk

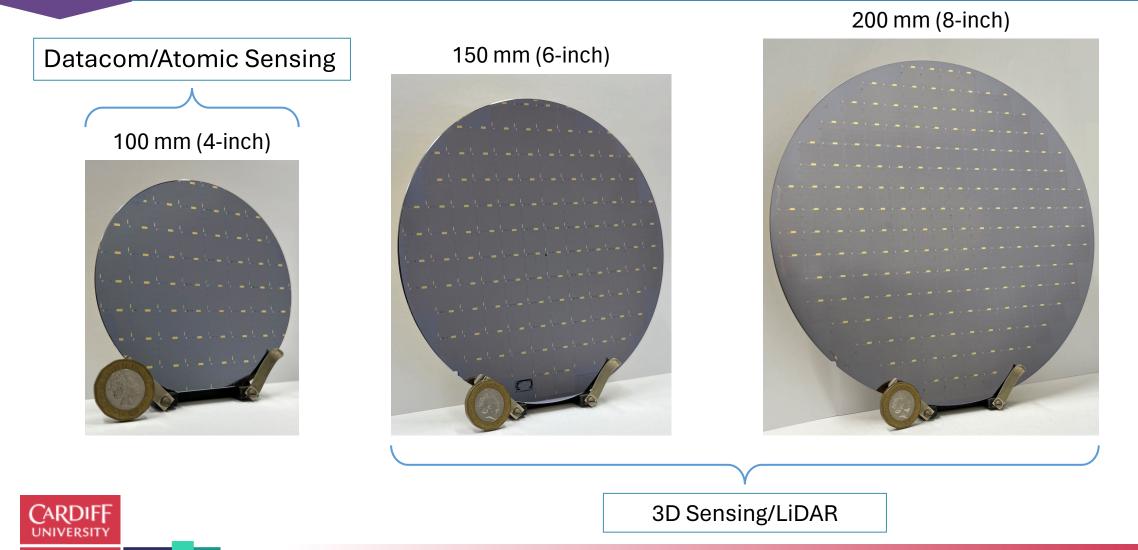

3D Sensing/LiDAR

#### Atomic Clocks/Magnetometers

| Device                        | Processing Time (Hours) |

|-------------------------------|-------------------------|

| Global N-Contact              | 24                      |

| Phase Cap-Etch                | 28                      |

| Co-Planar N-Contact           | 30                      |

| Full High-Performance Datacom | 264*                    |

\*Assumes 11 mask layers and 24 hours per mask layer as detailed in VCSEL Industry (2022)

Engineering and Physical Sciences Research Council

**EPSRC** Future Compound Semiconductor Manufacturing Hub

Datacom

100 mm (4-inch)

#### 150 mm (6-inch)

#### 200 mm (8-inch)

Engineering and Physical Sciences **Research Council**

bakerj19@cardiff.ac.uk

#### Wafer Diameters

Engineering and Physical Sciences Research Council

**Research Council**

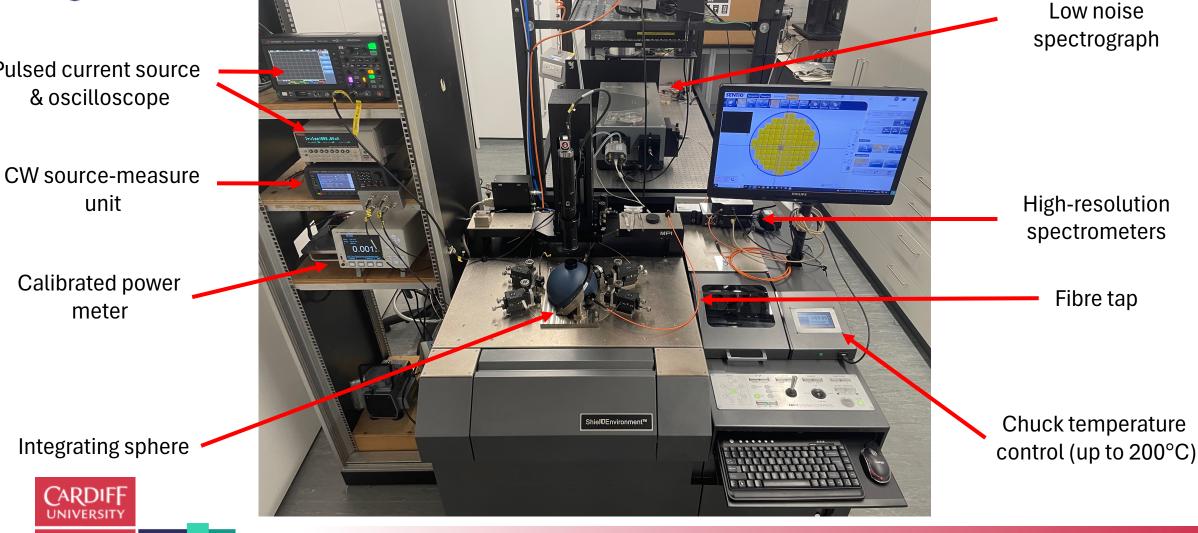

Pulsed current source & oscilloscope

unit

**Engineering and Physical Sciences Research Council**

bakerj19@cardiff.ac.uk

#### Adapt QuickSEL device structure <u>to allow</u> <u>wafer-scale analysis</u> of anti-phase structures and structures on semi-insulating substrates

Engineering and Physical Sciences Research Council

bakerj19@cardiff.ac.uk

| Market                         | Requirements                    | Growth                           | Device         | Where?    |

|--------------------------------|---------------------------------|----------------------------------|----------------|-----------|

| Sensing/LiDAR                  | High-power                      | Doped<br>substrate               | Global N       | [1]       |

| Atomic<br>clocks/magnetometers | Single-mode<br>Narrow linewidth | Anti-phase<br>cap                | Phase Cap-Etch | This work |

| Datacom                        | High-frequency modulation       | Semi-<br>insulating<br>substrate | Co-Planar N    | This work |

[1] "VCSEL Quick Fabrication for Assessment of Large Diameter Epitaxial Wafers," IEEE Phot. J, 14, 3, 1-10, (2022), doi:10.1109/JPHOT.2022.3169032.

Engineering and Physical Sciences Research Council

bakerj19@cardiff.ac.uk

**EPSRC** Future Compound Semiconductor Manufacturing Hub

NIVERSIT

ʹϡͼϗϽγϧ

Physical Sciences <u>bakerj19@cardiff.ac.uk</u> Research Council

| Market                         | Requirements                    | Growth                           | Device         | Where?    |

|--------------------------------|---------------------------------|----------------------------------|----------------|-----------|

| Sensing/LiDAR                  | High-power                      | Doped<br>substrate               | Global N       | [1]       |

| Atomic<br>clocks/magnetometers | Single-mode<br>Narrow linewidth | Anti-phase<br>cap                | Phase Cap-Etch | This work |

| Datacom                        | High-frequency modulation       | Semi-<br>insulating<br>substrate | Co-Planar N    | This work |

[1] "VCSEL Quick Fabrication for Assessment of Large Diameter Epitaxial Wafers," IEEE Phot. J, 14, 3, 1-10, (2022), doi:10.1109/JPHOT.2022.3169032.

24

Engineering and Physical Sciences ba Research Council

<u>bakerj19@cardiff.ac.uk</u>

Engineering and Physical Sciences Research Council

bakeri19@cardiff.ac.uk

Engineering and Physical Sciences Research Council

Physical Sciences Research Council

s bakerj19@cardiff.ac.uk

EPSRC Future Compound Semiconductor Manufacturing Hub

ʹ<sup>AE</sup>RDγ<sub>I</sub>₽

28

Physical Sciences <u>bakerj19@cardiff.ac.uk</u> Research Council

Engineering and Physical Sciences Research Council

bakerj19@cardiff.ac.uk

**EPSRC Future Compound Semiconductor Manufacturing Hub**

UNIVERSITY

PRIFYSGOL

ℨℰ℞ⅅℽⅅ

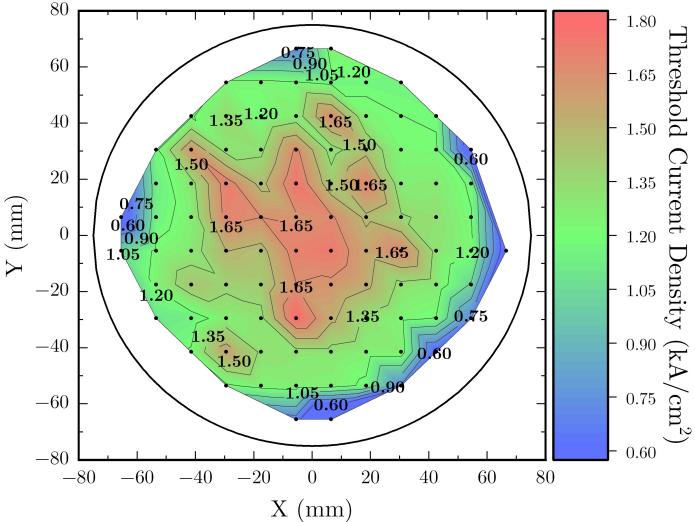

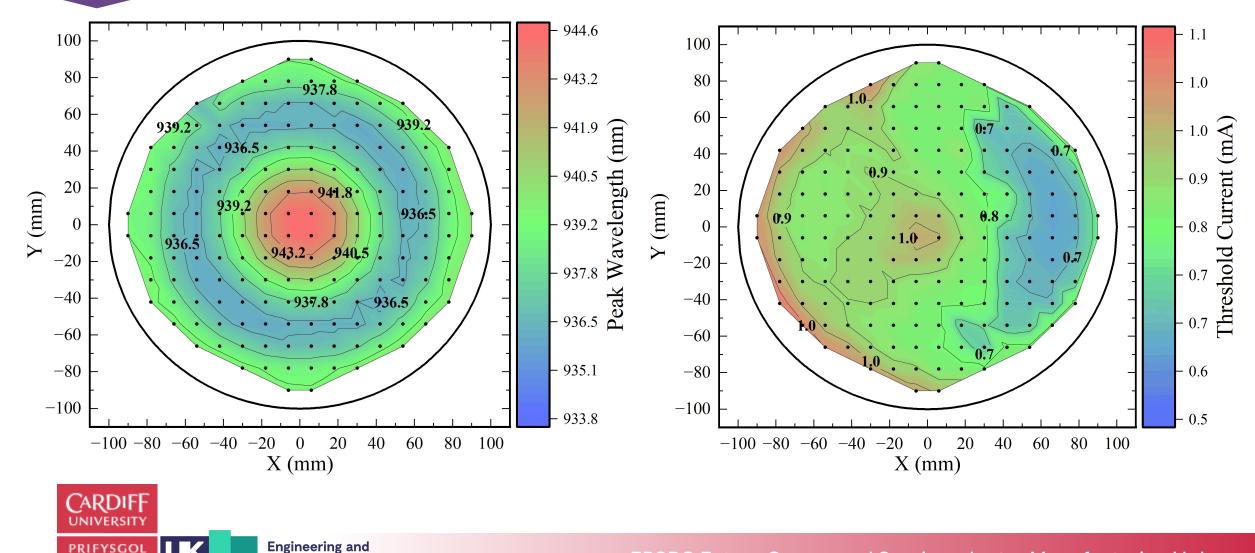

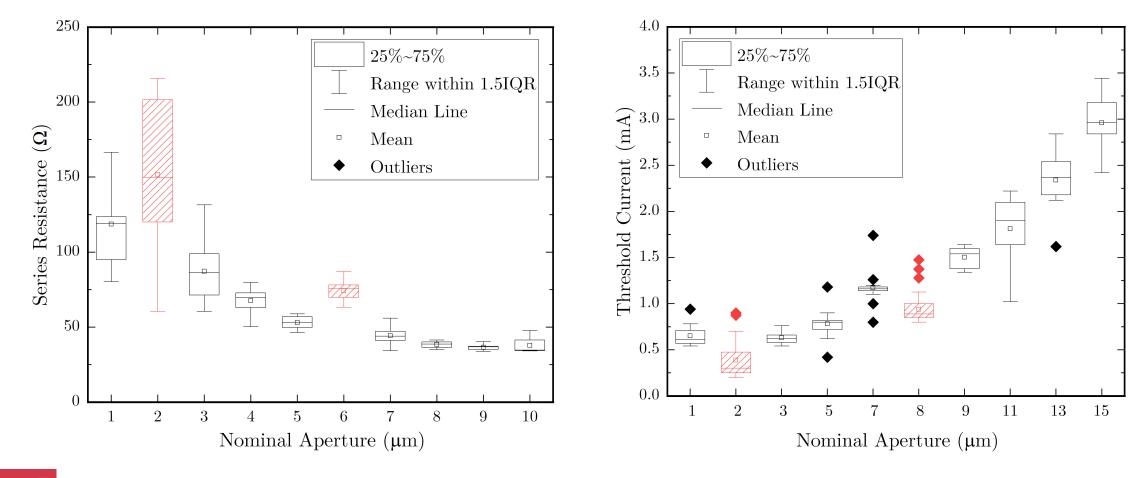

## Wafer-Scale Analysis – J<sub>th</sub>

bakerj19@cardiff.ac.uk

## Wafer-Scale Analysis – J<sub>th</sub>

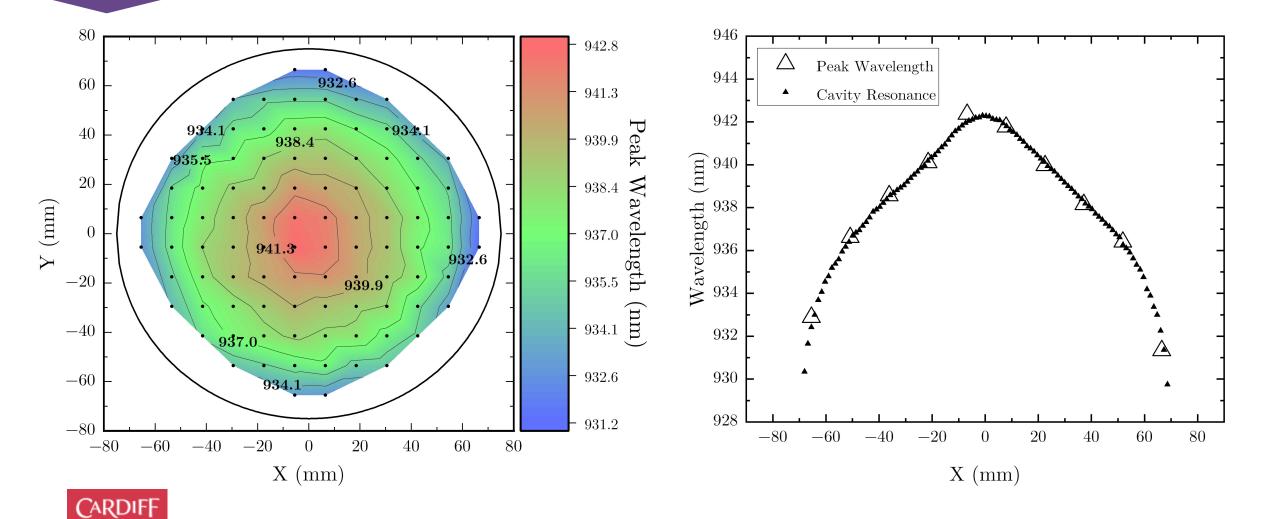

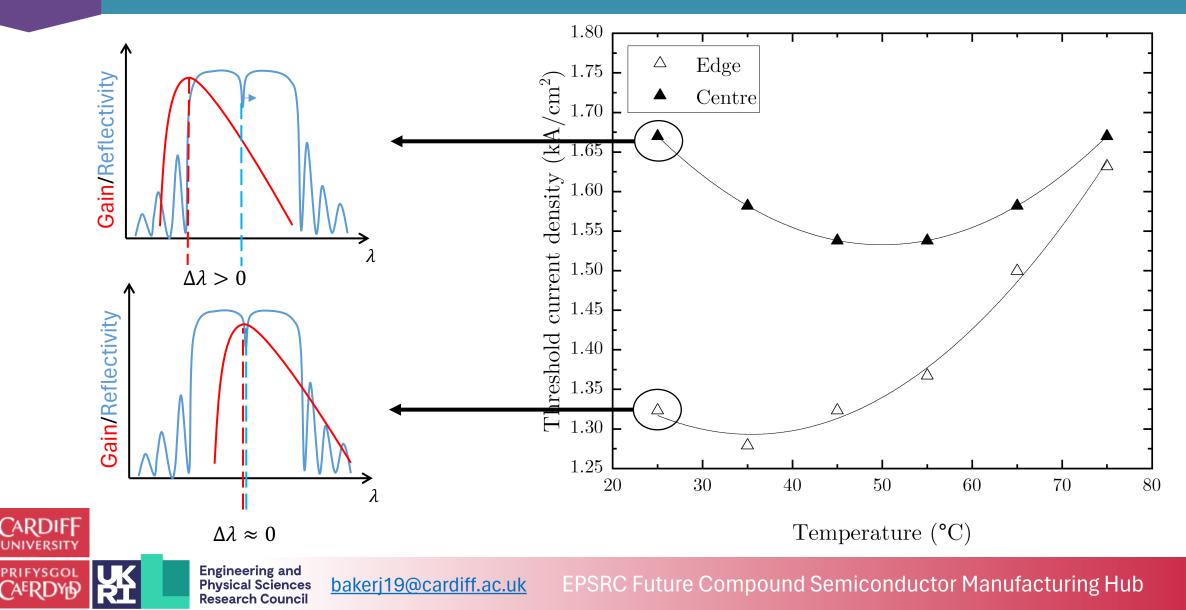

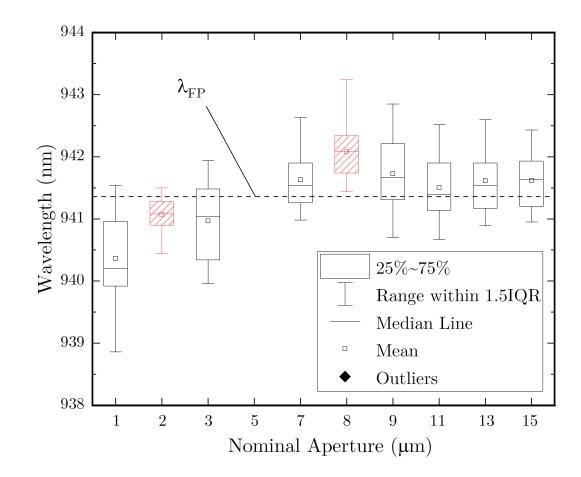

# Wafer-Scale Analysis – Gain Peak Detuning

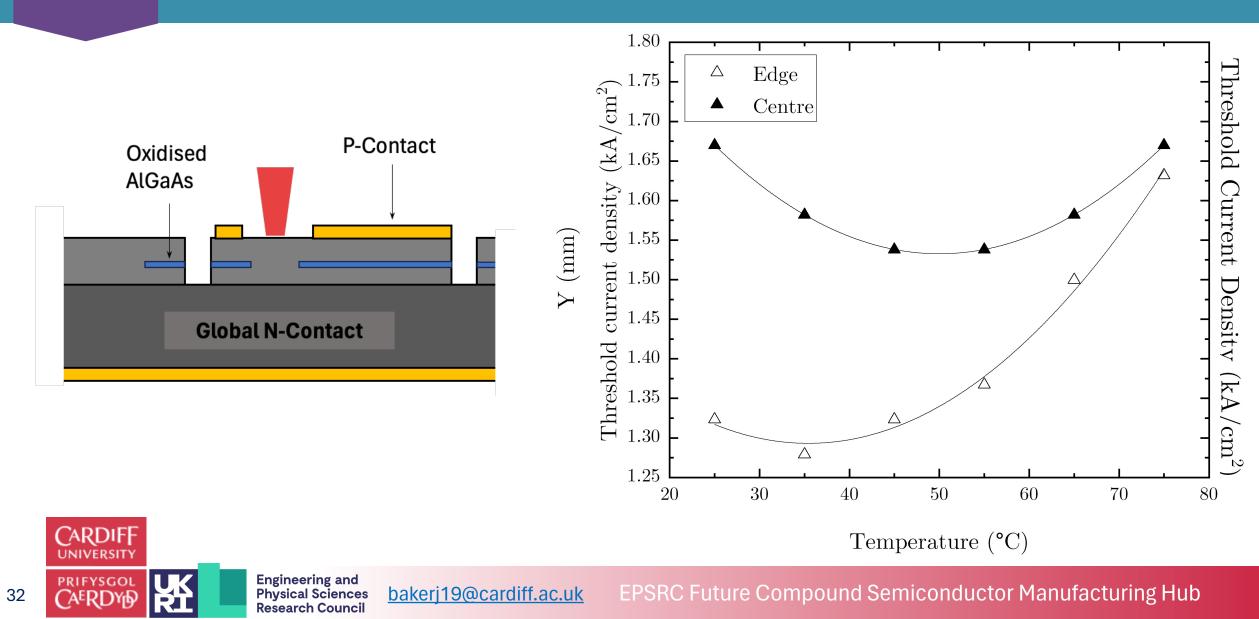

#### 200 mm Wafer Development

Physical Sciences <u>bakerj19@cardiff.ac.uk</u> Research Council **EPSRC Future Compound Semiconductor Manufacturing Hub**

ʹϡͼϗϽγϧ

RÌI

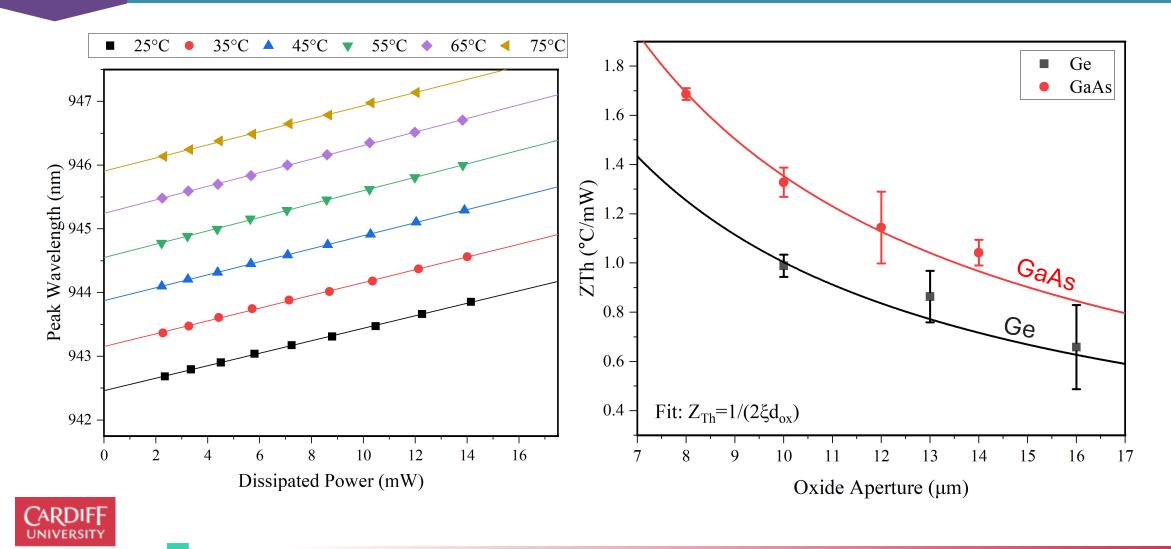

## VCSELs on Germanium (thermal performance vs GaAs)

Engineering and Physical Sciences Research Council

bakerj19@cardiff.ac.uk

**EPSRC** Future Compound Semiconductor Manufacturing Hub

RIFYSGO

#### VCSEL Product Development Cycle

**Research Council**

CS Hub

#### VCSEL Product Development Cycle

Physical Sciences Research Council <u>bakerj19@cardiff.ac.uk</u> EPSRC Future Compound Semiconductor Manufacturing Hub

CS Hub

Conclusion

Quick VCSELs (QuickSELs) which work for sensing/LiDAR, atomic clocks & magnetometers, and datacom applications

Total device processing time varies between 24 – 30 hours (versus 24 hours per mask layer)

Significantly reduces time required for feedback of VCSEL performance to epitaxy

38

**Engineering and** Physical Sciences **Research Council**

bakeri19@cardiff.ac.uk

#### Acknowledgements

Device fabrication was carried out by the European Regional Development Fund (ERDF)funded Institute for Compound Semiconductors (ICS) at Cardiff University.

This work was supported in part by:

- Engineering and Physical Sciences Research Council (EPSRC) Future Compound Semiconductor  $\geq$ Manufacturing Hub, under Grant EP/P006973/1

- $\succ$ European Regional Development Fund through SMART Expertise Project ATLAS, under Grant 82371.

- UKRI Strength in Places Fund, under Project 107134.  $\geq$

- Innovate UK OFoundry project.  $\succ$

**Research Council**

UK

Innovate

#### **National Physical Laboratory**

Cronfa Datblygu Rhanbarthol Ewrop **EU Funds: Investing in Wales** European Regional Development Fund

# Supplementary Info

Engineering and Physical Sciences Research Council

bakerj19@cardiff.ac.uk

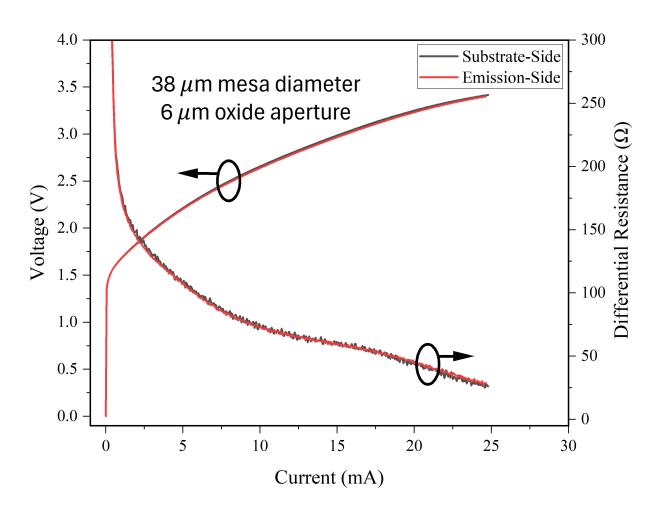

## QuickSEL – Initial Qualification

Engineering and Physical Sciences Research Council

# QuickSEL – Initial Qualification

Engineering and Physical Sciences Research Council

Engineering and Physical Sciences Research Council

bakerj19@cardiff.ac.uk

Engineering and Physical Sciences Research Council

**EPSRC Future Compound Semiconductor Manufacturing Hub**

PRIFYSGOL

Ĵ₄⁼RDγ₽

nces <u>bakerj19@cardiff.ac.uk</u>